Section 4 pipelining, 1 pipelines, Figure 4.1 basic pipelines – Renesas SH7781 User Manual

Page 95

4. Pipelining

Rev.1.00 Jan. 10, 2008 Page 65 of 1658

REJ09B0261-0100

Section 4 Pipelining

This LSI is a 2-ILP (instruction-level-parallelism) superscalar pipelining microprocessor.

Instruction execution is pipelined, and two instructions can be executed in parallel.

4.1

Pipelines

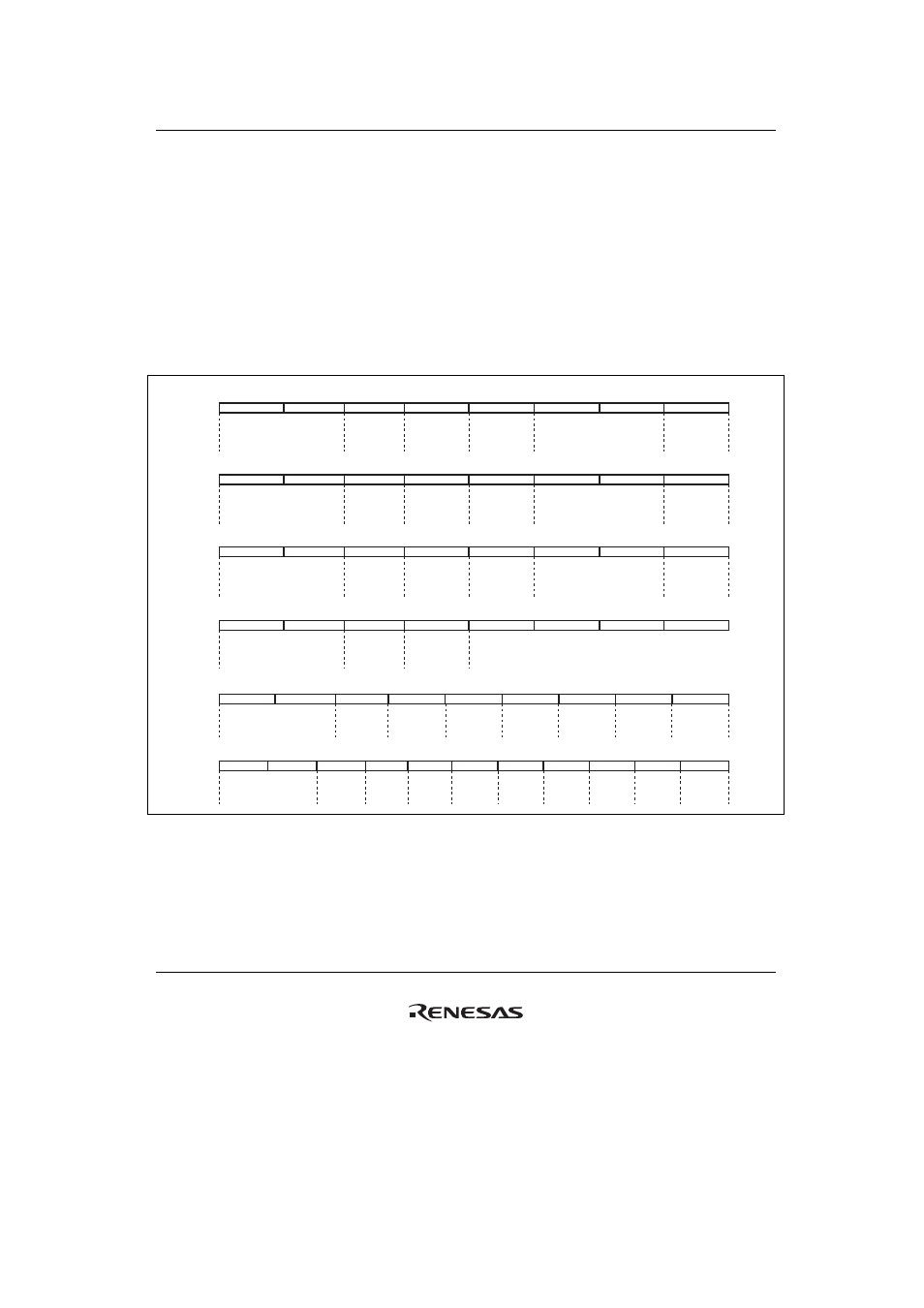

Figure 4.1 shows the basic pipelines. Normally, a pipeline consists of eight stages: instruction

fetch (I1/I2/I3), decode and register read (ID), execution (E1/E2/E3), and write-back (WB). An

instruction is executed as a combination of basic pipelines.

I1

I2

ID

E1

E2

E3

WB

I1

I2

ID

FS1

FS2

FS4

FS3

FS

I1

I2

I3

ID

FE1

FE2

FE3

FE4

FE5

FE6

FS

I1

I2

ID

E1

E2

E3

WB

I1

I2

ID

E1

E2

E3

WB

I1

I2

I3

I3

I3

I3

I3

ID

E1

E2

E3

WB

1. General Pipeline

-

Instruction fetch

-

Instruction

decode

-

Issue

-

Register read

-

Write-back

-

Operation

-

Forwarding

-

Address

calculation

2. General Load/Store Pipeline

3. Special Pipeline

4. Special Load/Store Pipeline

5. Floating-Point Pipeline

6. Floating-Point Extended Pipeline

-

Instruction fetch

-

Instruction

decode

-

Issue

-

Operation

-

Write-back

-

Operation

-

Operation

-

Register read

-

Forwarding

-

Operation

-

Instruction fetch

-Instruction

decode

-Issue

-Register read

-Forwarding

-

Operation

-

Operation

-

Operation

-

Operation

-

Operation

-

Operation

-

Write-back

-

Instruction fetch

-

Instruction

decode

-

Issue

-

Register read

-

Write-back

-

Memory data access

-

Forwarding

-

Instruction fetch

-

Instruction

decode

-

Issue

-

Register read

-

Write-back

-

Operation

-

Instruction fetch

-

Instruction

decode

-

Issue

-

Register read

-

Predecode

-

Predecode

-

Predecode

-

Predecode

-

Predecode

-

Predecode

Figure 4.1 Basic Pipelines