Renesas SH7781 User Manual

Page 614

13. PCI Controller (PCIC)

Rev.1.00 Jan. 10, 2008 Page 584 of 1658

REJ09B0261-0100

(25)

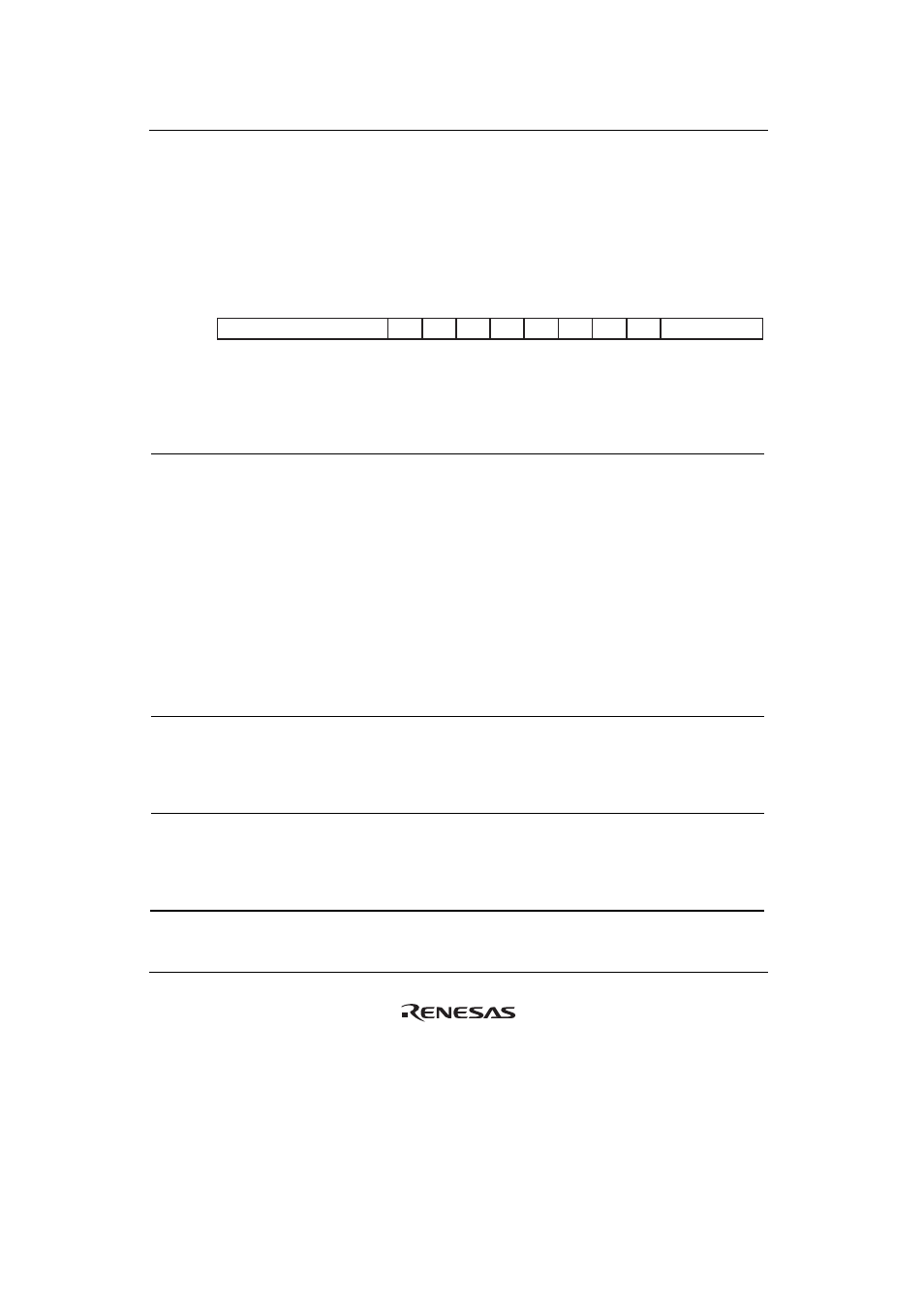

PCI Power Management Register (PCIPMC)

PCIPMC is a 16-bit register that provides information on the functions related to power

management. For details, see section 3, PCI Power Management Interface in PCI Bus Power

Management Interface Specification Revision 1.1. This register is not cleared by a power-on reset.

This register must be set during initialization of register initialization in the PCIC (CFINIT = 0 in

PCICR).

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

PMV

PMEC

⎯

DSI

⎯

⎯

⎯

D1S

D2S

PMCS

0

1

0

1

0

0

0

0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R

R

R

R

R

R/W

R/W

R

R

R

R

R

Bit:

Initial value:

SH R/W:

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

PCI R/W:

Bit Bit

Name

Initial

Value R/W

Description

15 to 11 PMCS

00000 SH: R

PCI: R

PME SUPPORT

This 5-bit field indicates the power state that asserts

PME, by using this power management function.

When these bits are 0, these bits indicate that this

function cannot assert

PME at that power state (not

supported).

(Bit11) xxxx1:

PME can be asserted from D0

(Bit12) xxx1x:

PME can be asserted from D1

(Bit13) xx1xx:

PME can be asserted from D2

(Bit14) x1xxx:

PME can be asserted from D3hot

(Bit15) 1xxxx:

PME can be asserted from D3cold

Note: The PCIC in this LSI dose not have the

PME

pin.

10 D2S 0 SH:

R/W

PCI: R

D2 Support

When this bit is 1, this power management function

supports the D2 power management state. When the

D2 power management state is not supported, this bit

should always be read as 0.

9 D1S 0

SH:

R/W

PCI: R

D1 Support

When this bit is 1, This function supports the D1

power management state. When the D1 power

management state is not supported, this bit is read as

0.