Renesas SH7781 User Manual

Page 49

1. Overview

Rev.1.00 Jan. 10, 2008 Page 19 of 1658

REJ09B0261-0100

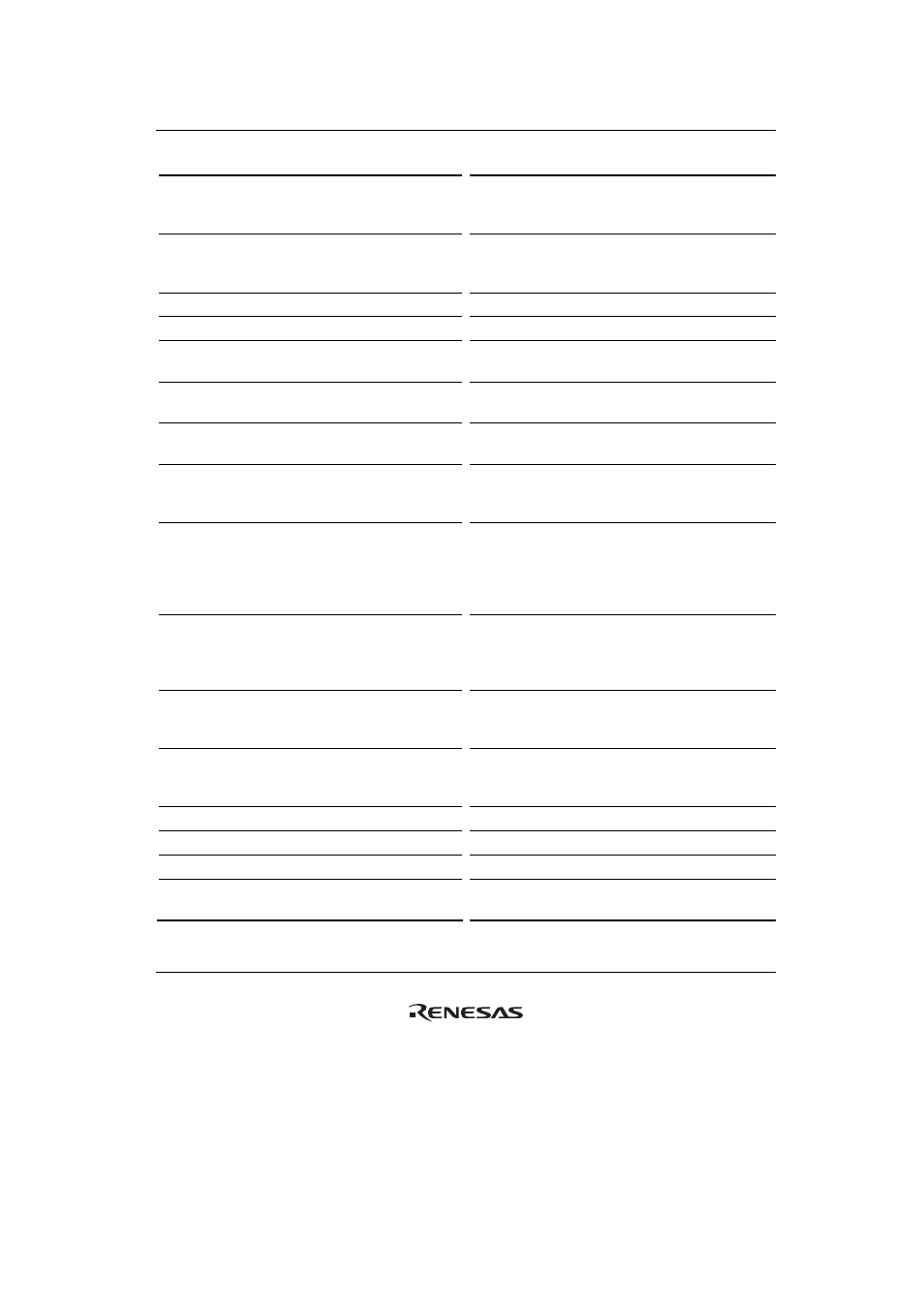

No. Pin Name

I/O

Function

No. Pin Name

I/O

Function

217

BREQ/BSACK I

Bus request (Master mode)/

Bus acknowledgement

(Slave mode)

233

ASEBRK/

BRKACK

I H-UDI

emulator

218

BACK/BSREQ O

Bus

acknowledgement

(Master mode)/Bus request

(Slave mode)

234 AUDCK

O

H-UDI emulator clock

219

DREQ0

I

DMA channel 0 request

235 AUDSYNC

O

H-UDI emulator

220

DREQ1

I

DMA channel 1 request

236 AUDATA0

O

H-UDI emulator data 0

221

DREQ2/INTB I/I

DMA

channel

2

request/PCI

interrupt B

237 AUDATA1

O

H-UDI emulator data 1

222

DREQ3/INTC I/I

DMA

channel

3

request/PCI

interrupt C

238 AUDATA2

O

H-UDI emulator data 2

223 DACK0

O

DMA channel 0 bus

acknowledgment

239 AUDATA3

O

H-UDI emulator data 3

224 DACK1

O

DMA channel 1 bus

acknowledgment

240 SCIF0_TXD/

HSPI_TX/

FWE

O/O/O SCIF0

transmit

data/HSPI

transmit data/NAND flash

write enable

225 DACK2/

SCIF2_TXD/

MMCCMD/

SIOF_TXD

O/O/O/I

O/O

DMA channel 2 bus

acknowledgment/SCIF2

transmit data/MMCIF

command response/SIOF

transmit data

241 SCIF0_RXD/

HSPI_RX/

FRB

I/I/I

SCIF0 receive data/HSPI

receive data/NAND flash

ready or busy

226 DACK3/

SCIF2_SCK/

MMCDAT/

SIOF_SCK

O/O/IO/

IO/IO

DMA channel 3 bus

acknowledgment/SCIF2

serial clock/MMCIF

data/SIOF serial clock

242 SCIF0_SCK/

HSPI_CLK/

FRE

IO/IO/O SCIF0 serial clock/HSPI

serial clock/NAND flash read

enable

227 DRAK2/

CE2A

O/O

DMA channel 2 transfer

request acknowledge

2/PCMCIA CE2A

243

SCIF0_RTS/

HSPI_CS/FSE

IO/IO/O SCIF0

modem

control/HSPI

chip selection/NAND flash

spare area enable

228 TCK

I

H-UDI clock

244

SCIF0_CTS/

INTD/FCE

IO/I/O SCIF0

modem

control/PCI

interrupt D/NAND flash chip

enable

229 TMS

I

H-UDI emulator

245 SCIF1_TXD O SCIF1

transmit

data

230 TDI

I

H-UDI data

246 SCIF1_RXD

I

SCIF1 receive data

231 TDO

O

H-UDI data

247 SCIF1_SCK

IO

SCIF1 serial clock

232

TRST I

H-UDI

emulator

248 SCIF2_RXD/

SIOF_RXD

I/I

SCIF2 receive data/SIOF

receive data