3 issue rates and execution cycles – Renesas SH7781 User Manual

Page 109

4. Pipelining

Rev.1.00 Jan. 10, 2008 Page 79 of 1658

REJ09B0261-0100

4.3

Issue Rates and Execution Cycles

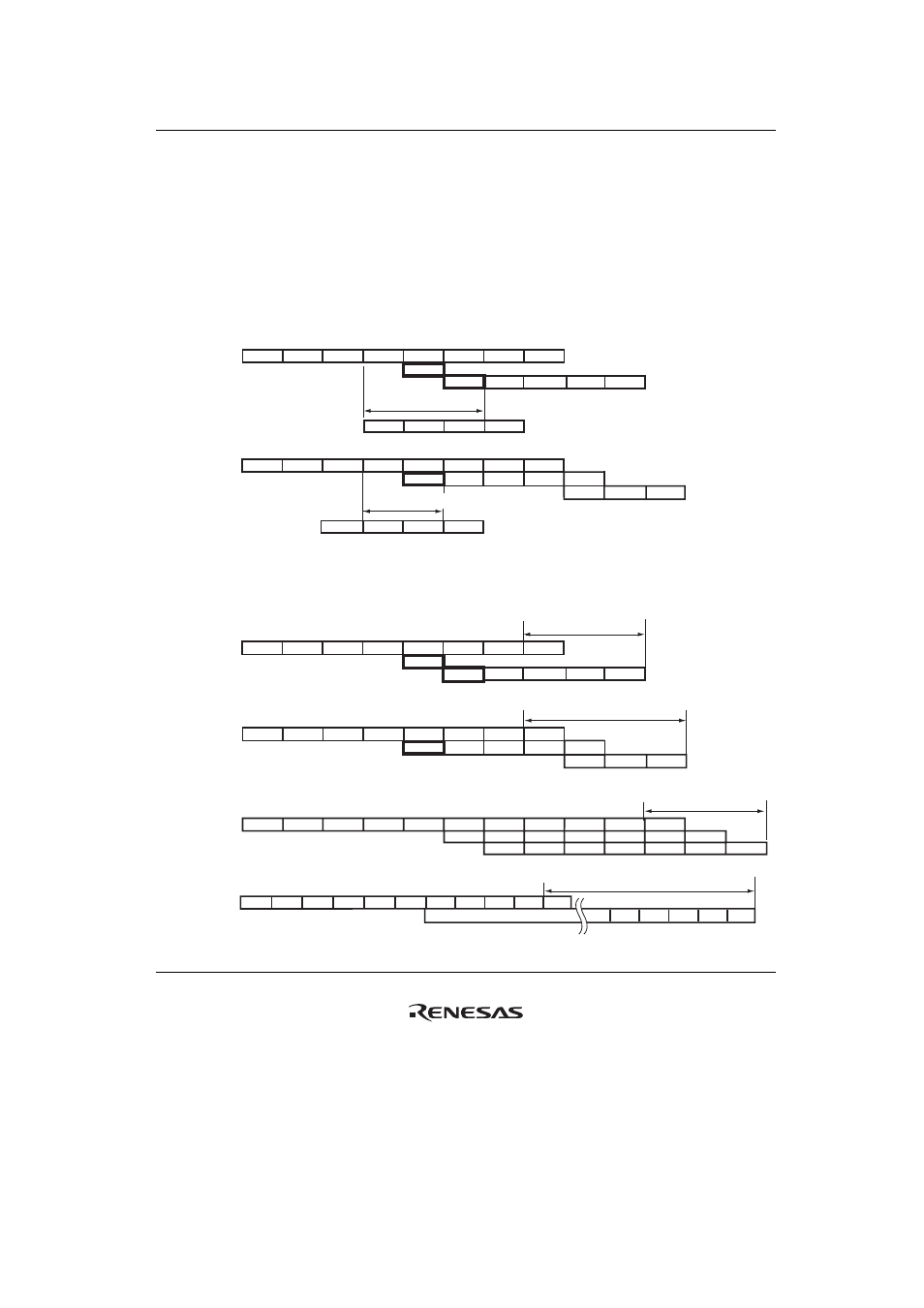

Instruction execution cycles are summarized in table 4.4. Instruction Group in the table 4.4

corresponds to the category in the table 4.2. Penalty cycles due to a pipeline stall are not

considered in the issue rates and execution cycles in this section.

I1

I2

I3

ID

S1

S2

S3

WB

E2S2

E3S3

WB

E1S1

I1

I2

I3

ID

S1

S2

S3

WB

MS

S2

S3

WB

S1

ID

ID

ID

(I1)

(ID)

(I2)

(I3)

M3

M2

(I1)

(I3)

(ID)

(I2)

I1

I2

I3

ID

S1

S2

S3

WB

E2S2

E3S3

WB

E1S1

ID

ID

I1

I2

I3

ID

S1

S2

S3

WB

MS

S2

S3

WB

S1

ID

M3

M2

FE1

FE2

FE3

FE4

FE5

FE6

FE1 FE2 FE3 FE4 FE5 FE6

FS

FE1

FE2

FE3

FE4

FE5

FE6

FS

FE1

FE2

FE3

FE4

FE5

FE6

FS

I1

I2

I3

ID

I1

I2

I3

ID

FS

FE3 FE4 FE5 FE6

FS

1. Issue Rate

Issue rate: 3

Issue rates indicates the issue period between one instruction and next instruction.

E.g. AND.B instruction

Next instruction

Issue rate: 2

E.g. MAC.W instruction

Execution cycles indicates the cycle counts an instruction occupied the pipeline based on the next rules.

CPU instruction

E.g. AND.B instruction

Execution Cycles: 3

E.g. MAC.W instruction

Execution Cycles: 4

2. Execution Cycles

Next instruction

FPU instruction

E.g. FMUL instruction

Execution Cycles: 14

E.g. FDIV instruction

Execution Cycles: 3

Divider occupation cycle