Renesas SH7781 User Manual

Page 711

14. Direct Memory Access Controller (DMAC)

Rev.1.00 Jan. 10, 2008 Page 681 of 1658

REJ09B0261-0100

14.3.7

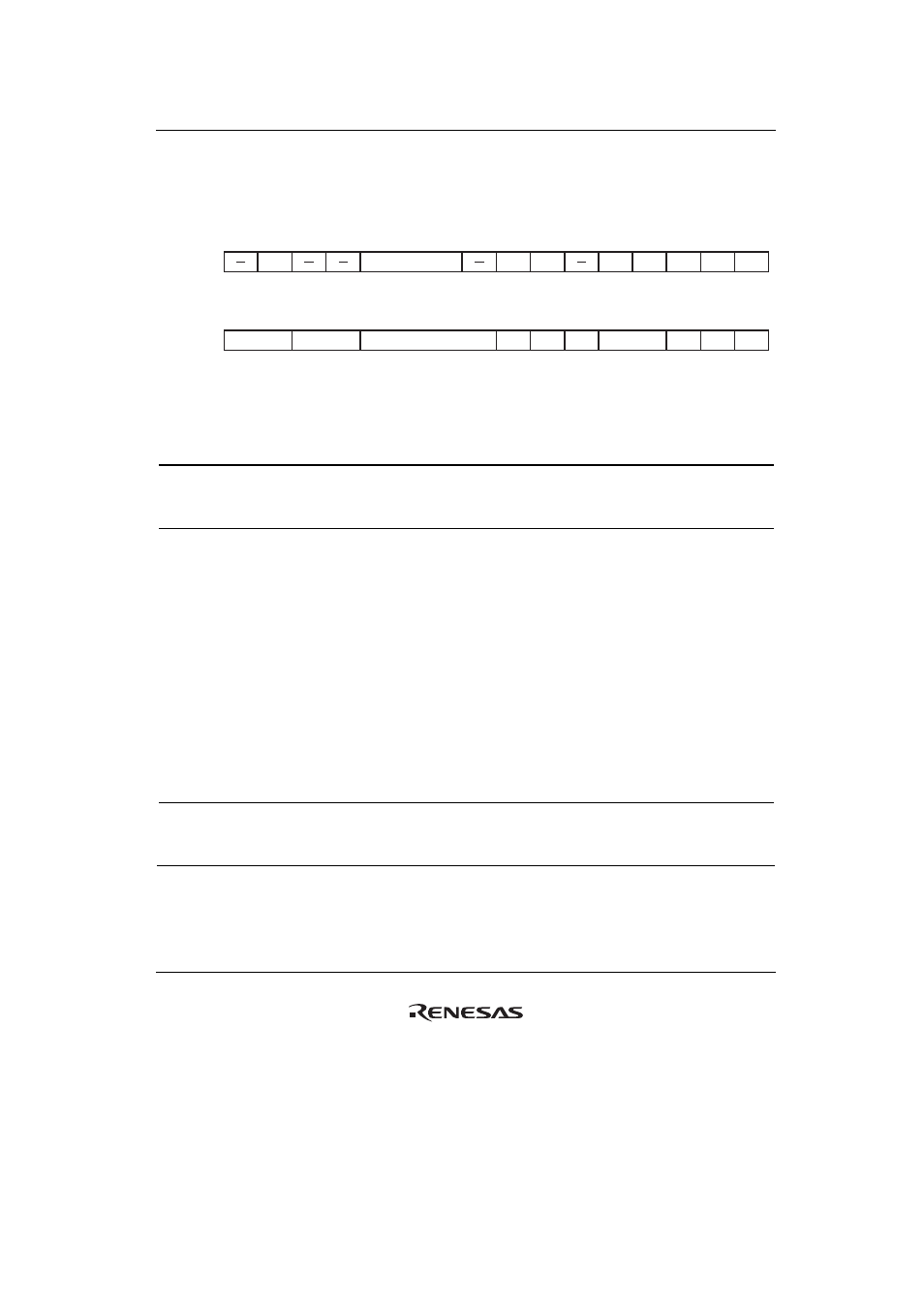

DMA Channel Control Registers 0 to 11 (CHCR0 to CHCR11)

CHCR are 32-bit readable/writable registers that control the DMA transfer mode.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R

R/W

R

R

R/W

R/W

R/W

R

R/W

R/W

R

R/W R/(W)* R/W

R/W

R/W

R/W

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W R/(W)*

Note: * R/(W): To clear the flag, 0 can be written to.

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

LCKN

RPT[2:0]

DO

RL

TS2

HE

HIE

AM

AL

DM[1:0]

SM[1:0]

RS[3:0]

DL

DS

TB

TS[1:0]

IE

TE

DE

Bit Bit

Name

Initial

Value R/W Descriptions

31

⎯ 0 R

Reserved

This bit is always read as 0. The write value should

always be 0.

30

LCKN

1

R/W

Bus Lock Signal Disable

Specifies whether the bus lock signal output is enabled

or disabled during a read instruction for the

SuperHyway bus. This bit is valid in cycle steal mode.

Clear this bit to 0 in burst mode.

If the bus lock signal is disabled, the bus request from

the bus master other than the DMAC can be accepted.

This can improve the bus usage efficiency in the

system.

For channels 0 to 5, this bit can be set to 0 or 1.

For channels 6 to 11, do not clear this bit to 0. The write

value should always be 1.

0: Bus lock signal output enabled

1: Bus lock signal output disabled

29, 28

⎯ All

0

R

Reserved

These bits are always read as 0. The write value should

always be 0.