Renesas SH7781 User Manual

Page 304

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 274 of 1658

REJ09B0261-0100

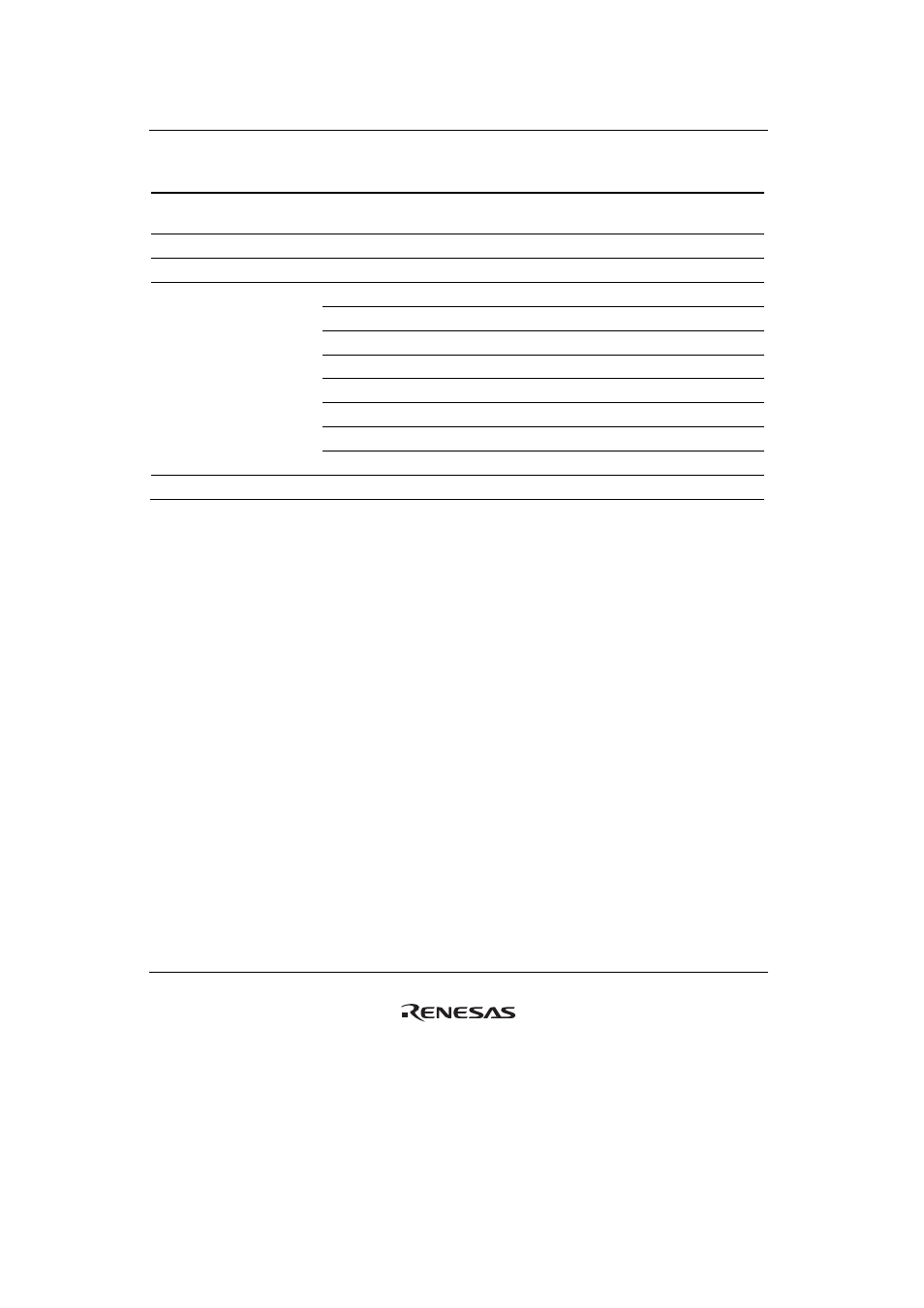

Name

Abbreviation

R/W

P4 Address

Area 7 Address

Access

Size

Sync.

Clock

Interrupt source register

(affected by the mask state)

INT2A1

R

H'FFD4 0034

H'1FD4 0034

32

Pck

Interrupt mask register

INT2MSKR

R/W

H'FFD4 0038

H'1FD4 0038

32

Pck

Interrupt mask clear register

INT2MSKCLR R/W

H'FFD4 003C

H'1FD4 003C

32

Pck

INT2B0

R

H'FFD4 0040

H'1FD4 0040

32

Pck

INT2B1

R

H'FFD4 0044

H'1FD4 0044

32

Pck

On-chip module interrupt

source registers

INT2B2

R

H'FFD4 0048

H'1FD4 0048

32

Pck

INT2B3

R

H'FFD4 004C

H'1FD4 004C

32

Pck

INT2B4

R

H'FFD4 0050

H'1FD4 0050

32

Pck

INT2B5

R

H'FFD4 0054

H'1FD4 0054

32

Pck

INT2B6

R

H'FFD4 0058

H'1FD4 0058

32

Pck

INT2B7

R

H'FFD4 005C

H'1FD4 005C

32

Pck

GPIO interrupt set register

INT2GPIC

R/W

H'FFD4 0090

H'1FD4 0090

32

Pck

Notes: 1. The interrupt source registers (INTREQ) are readable and conditionally writable

registers. For details, refer to section 10.3.1, External Interrupt Request Registers.

2. The NMI flag control register (NMIFCR) is readable and conditionally writable register.

For details, refer to section 10.3.1, External Interrupt Request Registers.