Renesas SH7781 User Manual

Page 342

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 312 of 1658

REJ09B0261-0100

(5)

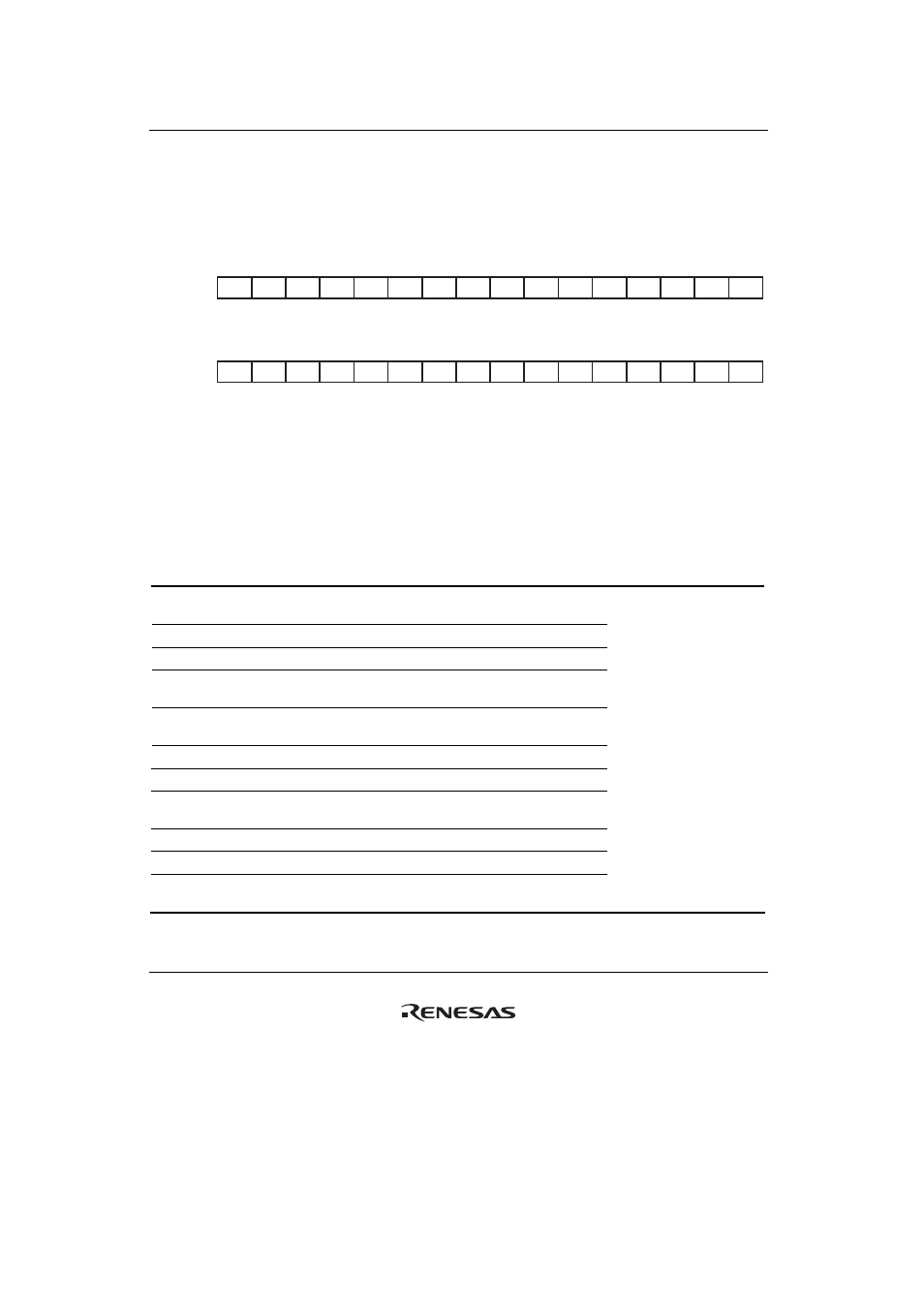

Interrupt Mask Clear Register (INT2MSKCR)

INT2MSKCR is a 32-bit write-only register that clears the masking set in the interrupt mask

register. When the corresponding bit in this register is set to 1, the interrupt source masking is

cleared. These bits are always read as 0.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

⎯

⎯

⎯

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R

R

Bit:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit:

Initial value:

R/W:

Table 10.10 shows the correspondence between bits in INT2MSKCR and interrupt masking that

are cleared.

Table 10.10 Correspondence between Bits in INT2MSKCR and Interrupt Masking that Are

Cleared

Bit

Initial

Value R/W Source

Function

Description

31 to

29

All 0

R

Reserved

These bits are always read as 0.

The write value should always be 0.

28

0

R/W GDTA

Clears the GDTA interrupt masking

27

0

R/W DU

Clears the DU interrupt masking

26

0

R/W SSI channel 1 Clears the SSI channel 1 interrupt

masking

25

0

R/W SSI channel 0 Clears the SSI channel 0 interrupt

masking

24

0

R/W GPIO

Clears the GPIO interrupt masking

Clears interrupt

masking for each on-

chip peripheral module

[When written]

0: Invalid

1: Clears interrupt

masking

[When read]

Always 0

23

0

R/W FLCTL

Clears the FLCTL interrupt masking

22

0

R/W MMCIF

Clears the MMCIF interrupt

masking

21

0

R/W HSPI

Clears the HSPI interrupt masking

20

0

R/W SIOF

Clears the SIOF interrupt masking

19

0

R/W PCIC (5)

Clears the PCIERR and PCIPWD3

to PCIPWD0 interrupts masking