10base-kr phy interfaces, 10base-kr phy interfaces -19 – Altera Transceiver PHY IP Core User Manual

Page 75

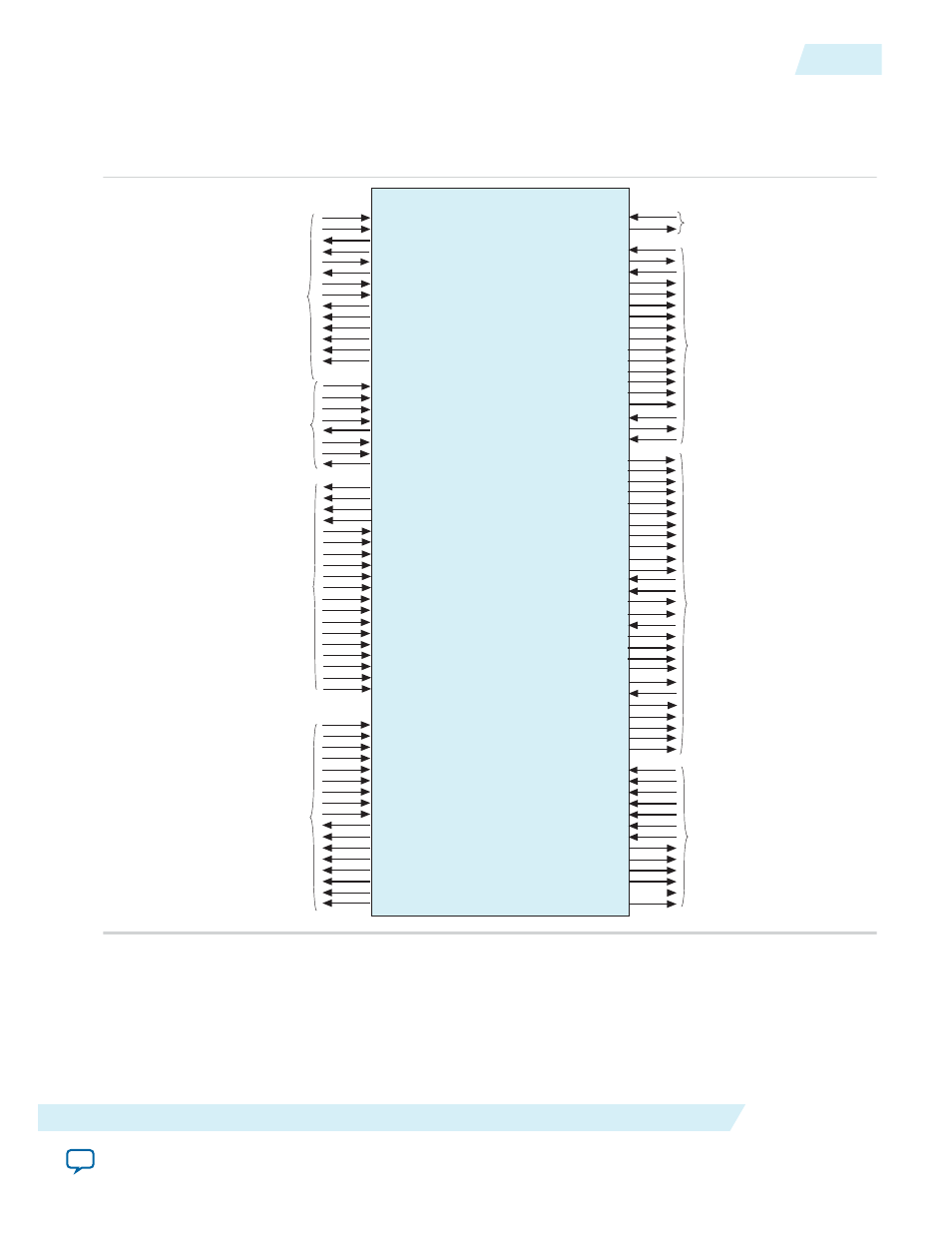

10BASE-KR PHY Interfaces

Figure 4-10: 10GBASE-KR Top-Level Signals

xgmii_tx_dc[71:0]

xgmii_tx_clk

xgmii_rx_dc[71:0]

xgmii_rx_clk

gmii_tx_d[7:0]

gmii_rx_d[7:0]

gmii_tx_en

gmii_tx_err

gmii_rx_err

gmii_rx_dv

led_char_err

led_link

led_disp_err

led_an

mgmt_clk

mgmt_clk_reset

mgmt_address[7:0]

mgmt_writedata[31:0]

mgmt_readdata[31:0]

mgmt_write

mgmt_read

mgmt_waitrequest

rx_recovered_clk

tx_clkout_1g

rx_clkout_1g

rx_coreclkin_1g

tx_coreclkin_1g

pll_ref_clk_1g

pll_ref_clk_10g

cdr_ref_clk_1g

cdr_ref_clk_10g

pll_powerdown_1g

pll_powerdown_10g

tx_analogreset

tx_digitalreset

rx_analogreset

rx_digitalreset

usr_an_lt_reset

usr_seq_reset

usr_fec_reset

usr_soft_10g_pcs_reset

upi_mode_en

upi_adj[1:0]

upe_inc

upi_dec

upi_pre

upi_init

upi_st_bert

upi_train_err

upi_lock_err

upi_rx_trained

upo_enable

upo_frame_lock

upo_cm_done

upo_bert_done

upo_ber_cnt[

upo_ber_max

upo_coef_max

10GBASE-KR Top-Level Signals

Dynamic

Reconfiguration

rx_serial_data

tx_serial_data

reconfig_to_xcvr[(

reconfig_from_xcvr[(

rc_busy

lt_start_rc

main_rc[5:0]

post_rc[4:0]

pre_rc[3:0]

tap_to_update[2:0]

seq_start_rc

pcs_mode_rc[5:0]

dfe_start_rc

dfe_mode[1:0]

ctle_start_rc

ctle_rc[3:0]

ctle_mode[1:0]

mode_1g_10gbar

en_lcl_rxeq

rx_block_lock

rxeq_done

rx_hi_ber

pll_locked

rx_is_lockedtodata

tx_cal_busy

rx_cal_busy

calc_clk_1g

rx_data_ready

rx_sync_status

tx_pcfifo_error_1g

rx_pcfifo_errog_1g

lcl_rf

tm_in_trigger[3:0]

tm_out_trigger[3:0]

rx_rlv

rx_clkslip

rx_latency_adj_1g[21:0]

tx_latency_adj_1g[21:0]

rx_latency_adj_10g[15:0]

tx_latency_adj_10g[15:0]

tx_frame

rx_clr_counters

rx_frame

rx_block_lock

rx_parity_good

rx_parity_invalid

rx_error_corrected

dmi_mode_en

dmi_frame_lock

dmi_rmt_rx_ready

dmi_lcl_coefl[5:0]

dmi_lcl_coefh[1:0]

dmi_lcl_upd_new

dmi_rx_trained

dmo_frame_lock

dmo_rmt_rx_ready

dmo_lcl_coefl[5:0]

dmo_lcl_coefh[1:0]

dmo_lcl_upd_new

dmo_rx_trained

Transceiver

Serial Data

XGMII

and GMII

Interfaces

Avalon-MM PHY

Management

Interface

Daisy Chain

Mode Input

Interface

(10GBASE-KR

Only)

Embedded

Processor

Interface

(10GBASE-KR

Only)

Clocks and

Reset

Interface

Status

The block diagram shown in the GUI labels the external pins with the interface type and places the

interface name inside the box. The interface type and name are used in the _hw.tcl file. If you turn on

Show signals, the block diagram displays all top-level signal names. For more information about _hw.tcl

files, refer to refer to the Component Interface Tcl Reference chapter in volume 1 of the Quartus II

Handbook

UG-01080

2015.01.19

10BASE-KR PHY Interfaces

4-19

Backplane Ethernet 10GBASE-KR PHY IP Core with Early Access FEC Option

Altera Corporation