Altera Transceiver PHY IP Core User Manual

Page 209

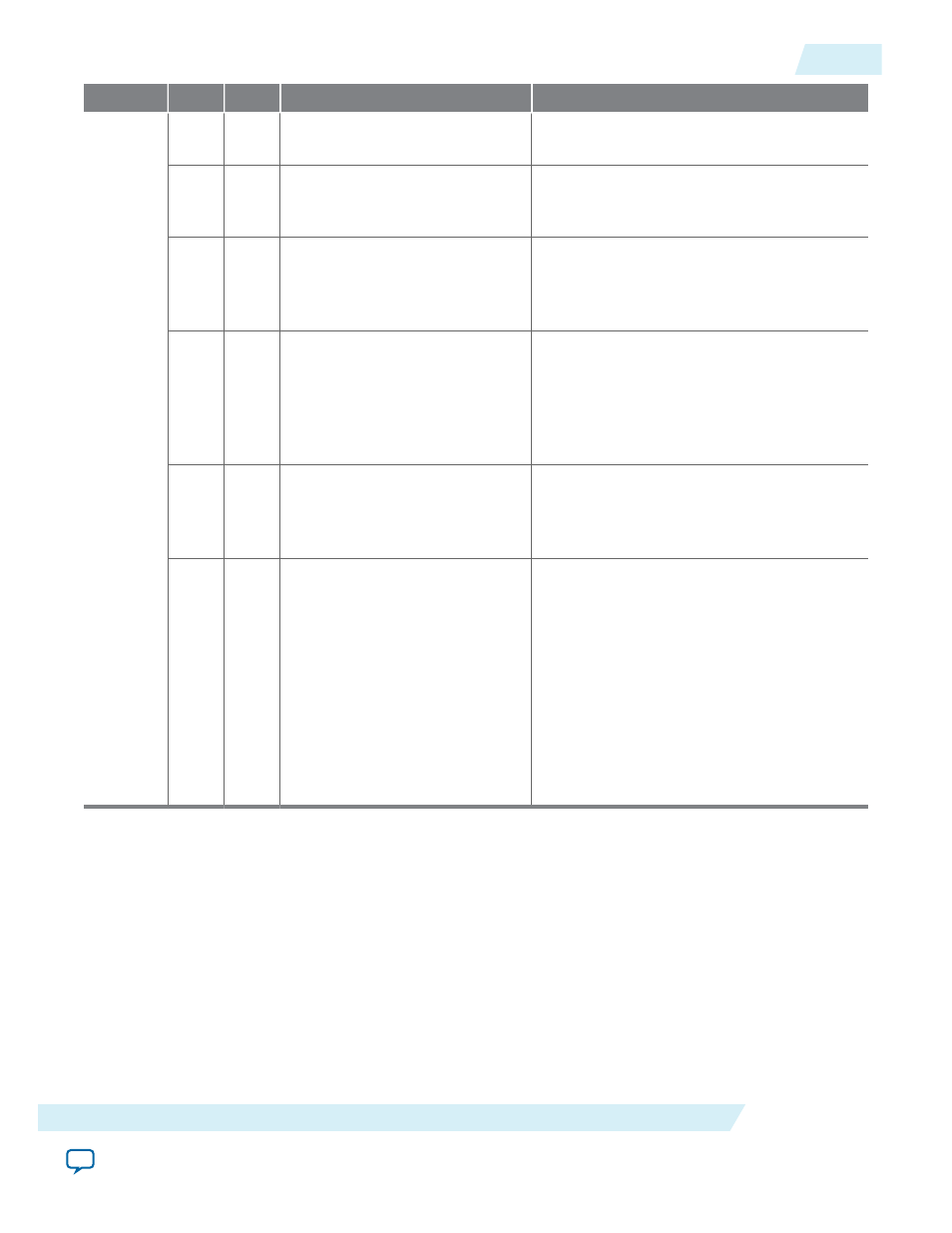

Word Addr

Bits

R/W

Register Name

Description

0x086

[31:20

]

R

Reserved

—

[19:16

]

R

rx_rlv

When set, indicates a run length violation.

From block: Word aligner.

[15:12

]

R

rx_patterndetect

When set, indicates that RX word aligner

has achieved synchronization.

From block: Word aligner.

[11:8] R

rx_disperr

When set, indicates that the received 10-bit

code or data group has a disparity error.

When set, the corresponding errdetect bits

are also set.

From block: 8B/10B decoder.

[7:4]

R

rx_syncstatus

When set, indicates that the RX interface is

synchronized to the incoming data.

From block: Word aligner.

[3:0]

R

rx_errdetect

When set, indicates that a received 10-bit

code group has an 8B/10B code violation or

disparity error. It is used along with RX

disparity to differentiate between a code

violation error and a disparity error, or

both.

In PIPE mode, the PIPE specific output

port called

pipe_rxstatus

encodes the

errors.

From block: 8B/10B decoder.

For more information about the individual PCS blocks, refer to Transceiver Architecture in Stratix V

Devices in the Stratix V Device Handbook.

Related Information

PHY for PCIe (PIPE) Link Equalization for Gen3 Data Rate

Gen3 requires both TX and RX link equalization because of the data rate, the channel characteristics,

receiver design, and process variations. The link equalization process allows the Endpoint and Root Port

to adjust the TX and RX setup of each lane to improve signal quality. This process results in Gen3 links

with a receiver Bit Error Rate (BER) that is less than 10

-12

.

UG-01080

2015.01.19

PHY for PCIe (PIPE) Link Equalization for Gen3 Data Rate

8-21

PHY IP Core for PCI Express (PIPE)

Altera Corporation