Altera Transceiver PHY IP Core User Manual

Page 193

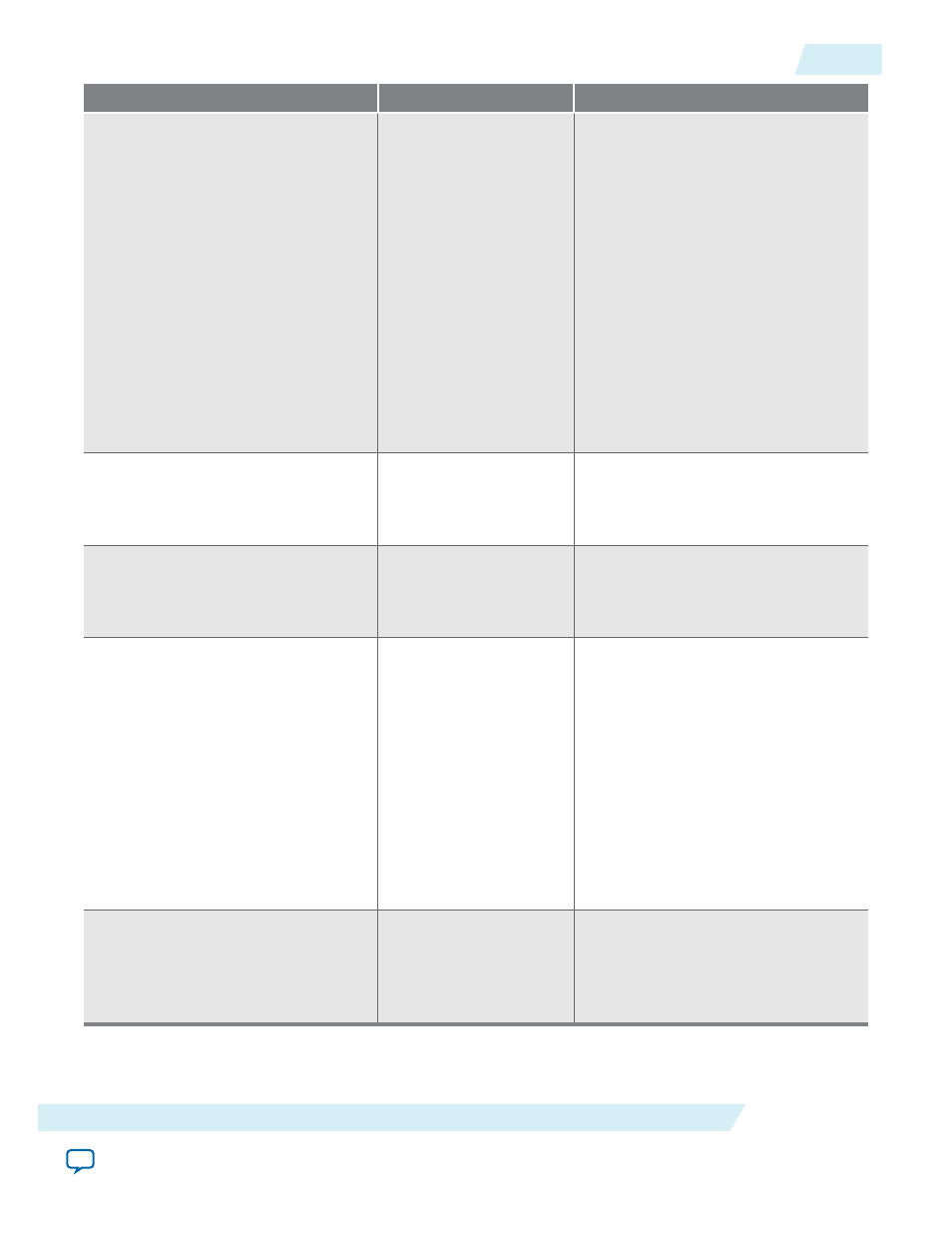

Name

Value

Description

Gen1 and Gen2 PLL type

CMU

ATX

You can select either the CMU or

ATX PLL. The CMU PLL has a larger

frequency range than the ATX PLL.

The ATX PLL is designed to improve

jitter performance and achieves lower

channel-to-channel skew; however, it

supports a narrower range of data

rates and reference clock frequencies.

Another advantage of the ATX PLL is

that it does not use a transceiver

channel, while the CMU PLL does.

Gen3 variants require 2 PLLs for link

training which begins in Gen1 and

negotiates up to Gen3 if both sides of

the link are Gen3 capable.

Gen3 PLL type

ATX

Gen3 uses the ATX PLL because its

jitter characteristics are better than

the CMU PLL for data rates above 6

Gbps.

PLL reference clock frequency

100 MHz

125 MHz

You can use either the 100 MHz or

125 MHz input reference clock. (The

PCI Express specifications, require an

100 MHz reference clock.)

FPGA transceiver width

8, 16, 32

Specifies the width of the interface

between the PHY MAC and PHY

(PIPE).The following options are

available:

• Gen1: 8 or 16 bits

• Gen2: 16 bits

• Gen3: 32 bits

Using the Gen1 16-bit interface

reduces the required clock frequency

by half at the expense of extra FPGA

resources.

Run length

5–160

Specifies the maximum number of

consecutive 0s or 1s that can occur in

the data stream. The

rx_rlv

signal is

asserted if the maximum run length is

violated.

Related Information

•

UG-01080

2015.01.19

PHY for PCIe (PIPE) General Options Parameters

8-5

PHY IP Core for PCI Express (PIPE)

Altera Corporation