Interlaken phy avalon-st tx interface, Interlaken phy avalon-st tx interface -7 – Altera Transceiver PHY IP Core User Manual

Page 174

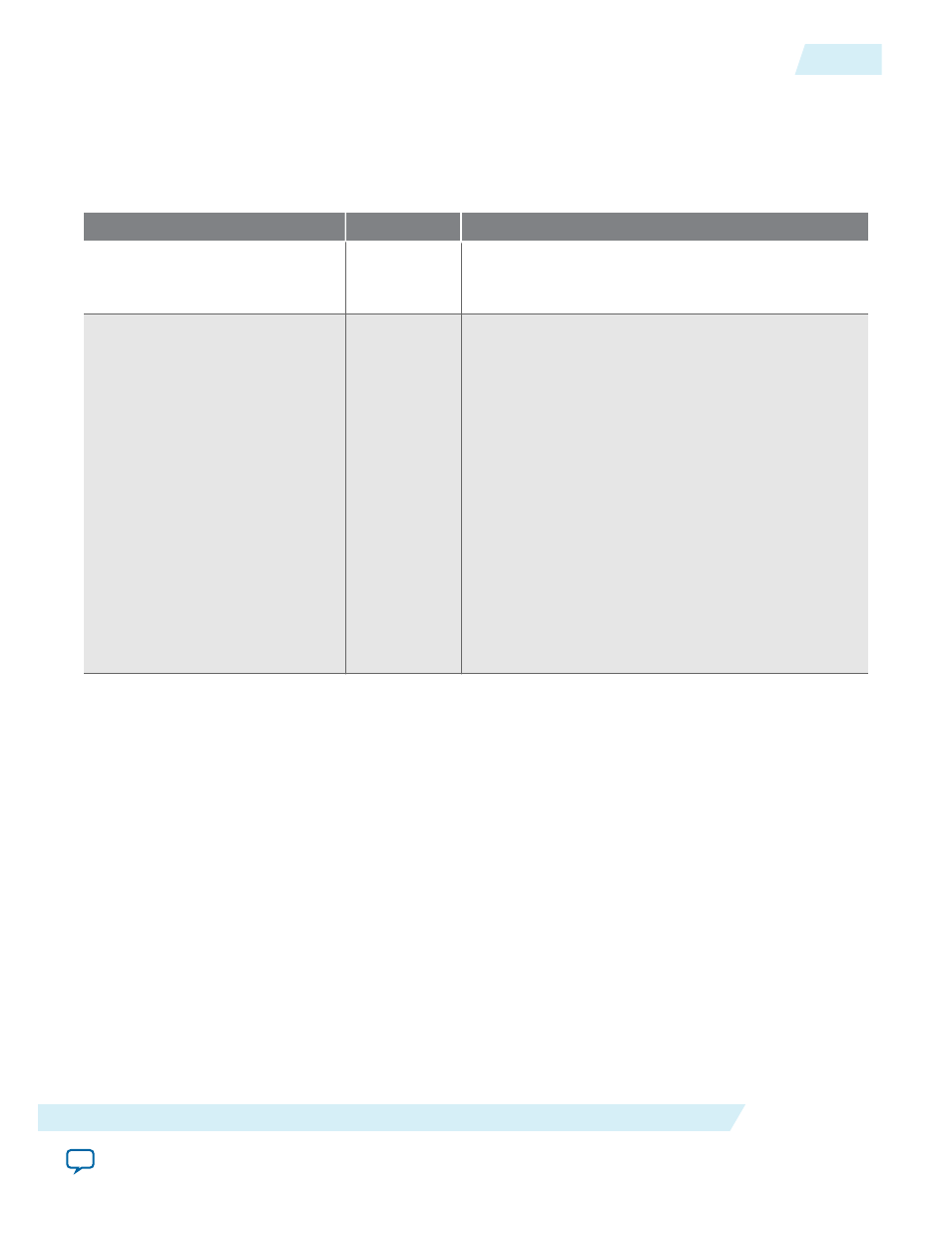

Interlaken PHY Avalon-ST TX Interface

This section lists the signals in the Avalon-ST TX interface.

Table 7-4: Avalon-ST TX Signals

Signal Name

Direction

Description

tx_parallel_data

Input

Avalon-ST data bus driven from the FPGA fabric to

the TX PCS. This input should be synchronized to the

tx_coreclkin

clock domain.

tx_parallel_data

Input

Indicates whether

tx_parallel_data

represents control or data. When deasserted,

tx_

parallel_data

is a data word. When

asserted,

tx_parallel_data

is a control

word.

The value of header synchronization bits[65:64] of the

Interlaken word identify whether bits[63:0] are a

Framing Layer Control/Burst/IDLE Control Word or

a data word. The MAC must gray encode the header

synchronization bits. The value 2'b10 indicating

Burst/IDLE Control Word must be gray encoded to

the value 1'b1 for

tx_parallel_data

. The

value 2'b01 indicating data word must be gray

encoded to the value 1'b0 for

tx_parallel_data

[64]

. You can also tie header synchronization bit[65]

to

tx_parallel_data[64]

directly.

UG-01080

2015.01.19

Interlaken PHY Avalon-ST TX Interface

7-7

Interlaken PHY IP Core

Altera Corporation