Simulation support, Slew rate settings, Simulation support -76 – Altera Transceiver PHY IP Core User Manual

Page 374: Slew rate settings -76

Example 12-5: Overriding Logical Channel 0 Channel Assignment Restrictions in Stratix V

Device for ×6 or ×N Bonding

If you are using ×6 or ×N bonding, transceiver dynamic reconfiguration requires that you assign

the starting channel number. Logical channel 0 should be assigned to either physical transceiver

channel 1 or channel 4 of a transceiver bank. However, if you have already created a PCB with a

different lane assignment for logical lane 0, you can use the workaound shown in the following

example to remove this restriction. The following example redefines the pma_bonding_master

parameter using the Quartus II Assignment Editor. In this example, the pma_bonding_master

was originally assigned to physical channel 1. (The original assignment could also have been to

physical channel 4.) The to parameter reassigns the pma_bonding_master to the Deterministic

Latency PHY instance name. You must substitute the instance name from your design for the

instance name shown in quotation marks

set_parameter -name pma_bonding_master "\"1\"" -to "

Simulation Support

The Quartus II release provides simulation and compilation support for the Stratix V Native PHY IP

Core. Refer to Running a Simulation Testbench for a description of the directories and files that the

Quartus II software creates automatically when you generate your Stratix V Transceiver Native PHY IP

Core.

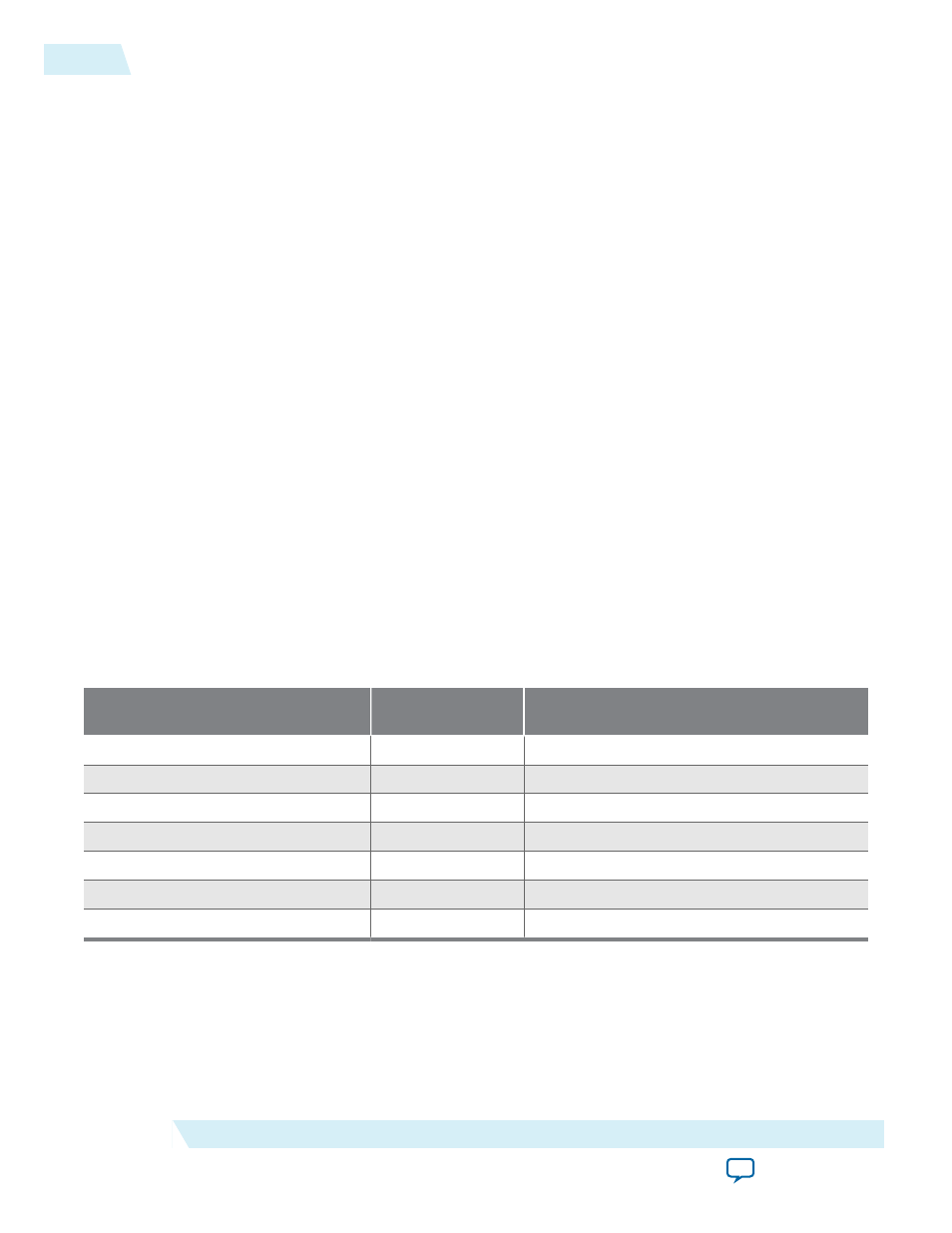

Slew Rate Settings

The following transceiver slew rate settings are allowed in Quartus II software. These settings are

applicable for Stratix V and Arria V GZ devices.

Protocol / Datarate

Allowed Quartus II

Settings

IBIS-AMI Setting

PCI Express Gen3, Gen2, CEI

4

*_30ps

PCI Express Gen1, XAUI

3

*_50ps

Gigabit Ethernet

1

*_160ps

=<1 Gbps

1,2,3

*_160ps, *_90ps, *_50ps

1 Gbps - 3 Gbps

2,3

*_90ps, *_50ps

>3 Gbps - 6 Gbps

3,4

*_50ps, *_30ps

>6 Gbps

4,5

*_30ps, *_15ps

Assigning an invalid slew rate will result in an error message similar to the one below:

Error (15001): Assignment XCVR_TX_SLEW_RATE_CTRL of value "4" conflicts with the valid

parameter values for pm_tx_slew_rate_ctrl

12-76

Simulation Support

UG-01080

2015.01.19

Altera Corporation

Stratix V Transceiver Native PHY IP Core