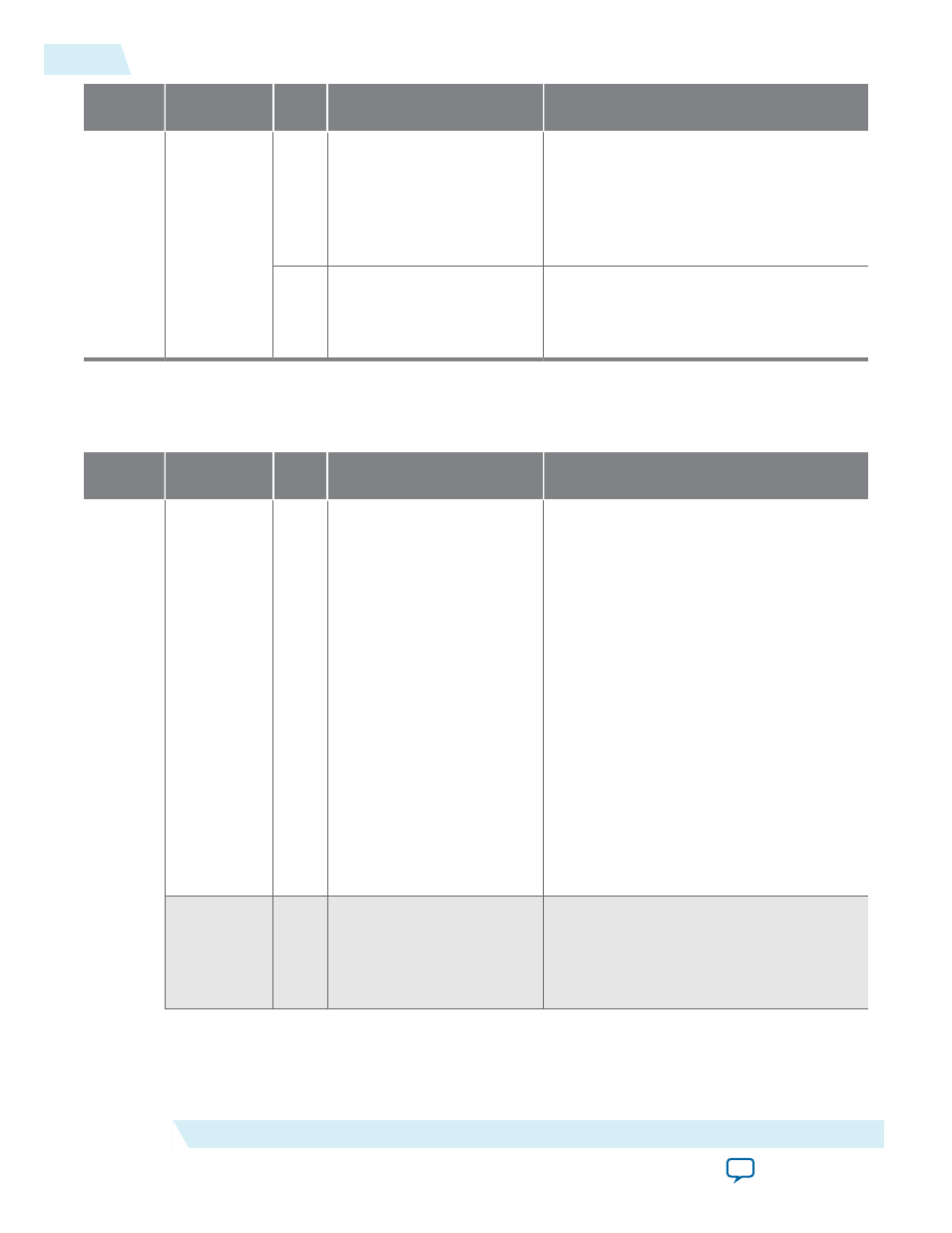

Reset controls –manual mode – Altera Transceiver PHY IP Core User Manual

Page 243

Word

Addr

Bits

R/W

Register Name

Description

0x042

[1:0]

W

reset_control

(write)

Writing a 1 to bit 0 initiates a TX digital

reset using the reset controller module.

The reset affects channels enabled in the

reset_ch_bitmask

. Writing a 1 to bit 1

initiates a RX digital reset of channels

enabled in the

reset_ch_bitmask

.

R

reset_status

(read)

Reading bit 0 returns the status of the

reset controller TX ready bit. Reading bit

1 returns the status of the reset controller

RX ready bit.

Reset Controls –Manual Mode

Table 9-23: Reset Controls –Manual Mode

Word

Addr

Bits

R/W

Register Name

Description

0x044

[31:0]

[31:4,0] are

reserved

RW

reset_fine_control

You can use the

reset_fine_control

register to create your own reset sequence.

If you disable Enable embedded reset

controller on the General Options tab of

the MegaWizard Plug-In Manager, you

can design your own reset sequence using

the

tx_analogreset

,

rx_analogreset

,

tx_digitalreset

,

rx_digitalreset

,

and

pll_powerdown

which are top-level

ports of the Custom Transceiver PHY. By

default, the CDR circuitry is in automatic

lock mode whether you use the embedded

reset controller or design your own reset

logic. You can switch the CDR to manual

mode by writing the

pma_rx_setlockto-

data

or

pma_rx_set_locktoref

registers

to 1.

It is safe to write 0s to reserved bits.

[3]

RW

reset_rx_digital

Writing a 1 causes the internal RX digital

reset signal to be asserted, resetting the

RX digital channels enabled in

reset_ch_

bitmask

. You must write a 0 to clear the

reset condition.

9-30

Reset Controls –Manual Mode

UG-01080

2015.01.19

Altera Corporation

Custom PHY IP Core