Optional status interface, Optional status interface -24 – Altera Transceiver PHY IP Core User Manual

Page 237

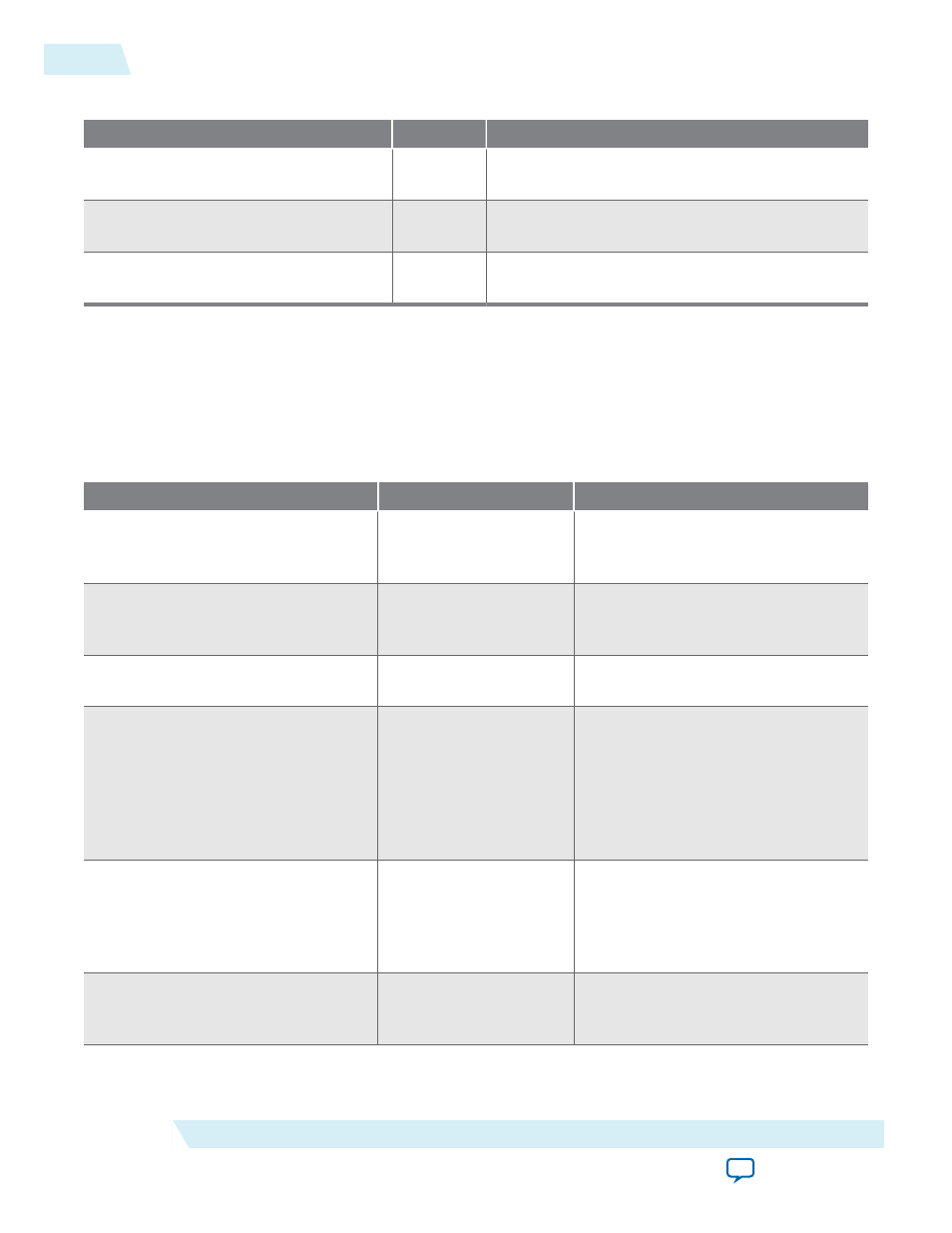

Table 9-17: Clock Signals

Signal Name

Direction

Description

pll_ref_clk

Input

Reference clock for the PHY PLLs. Frequency

range is 50-700 MHz.

rx_coreclkin[

Input

This is an optional clock to drive the coreclk of the

RX PCS.

tx_coreclkin[

Input

This is an optional clock to drive the coreclk of the

TX PCS

Related Information

on page 9-19

Optional Status Interface

This topic describes the optional status signals for the TX and RX interface.

Table 9-18: Serial Interface and Status Signals

Signal Name

Direction

Signal Name

tx_ready

Output

When asserted, indicates that the TX

interface has exited the reset state and

is ready to transmit.

rx_ready

Output

When asserted, indicates that the RX

interface has exited the reset state and

is ready to receive.

pll_locked[

-1:0]

Output

When asserted, indicates that the PLL

is locked to the input reference clock.

tx_forceelecidle[

Input

When asserted, enables a circuit to

detect a downstream receiver. It is

used for the PCI Express protocol.

This signal must be driven low when

not in use because it causes the TX

PMA to enter electrical idle mode and

tristate the TX serial data signals.

tx_bitslipboundaryselect [

1:0]

Input

This signal is used for bit slip word

alignment mode. It selects the

number of bits that the TX block

must slip to achieve a deterministic

latency.

rx_disperr[)-1:0]

Output

When asserted, indicates that the

received 10-bit code or data group

has a disparity error.

9-24

Optional Status Interface

UG-01080

2015.01.19

Altera Corporation

Custom PHY IP Core