Register interface and register descriptions, Register interface and register descriptions -27 – Altera Transceiver PHY IP Core User Manual

Page 240

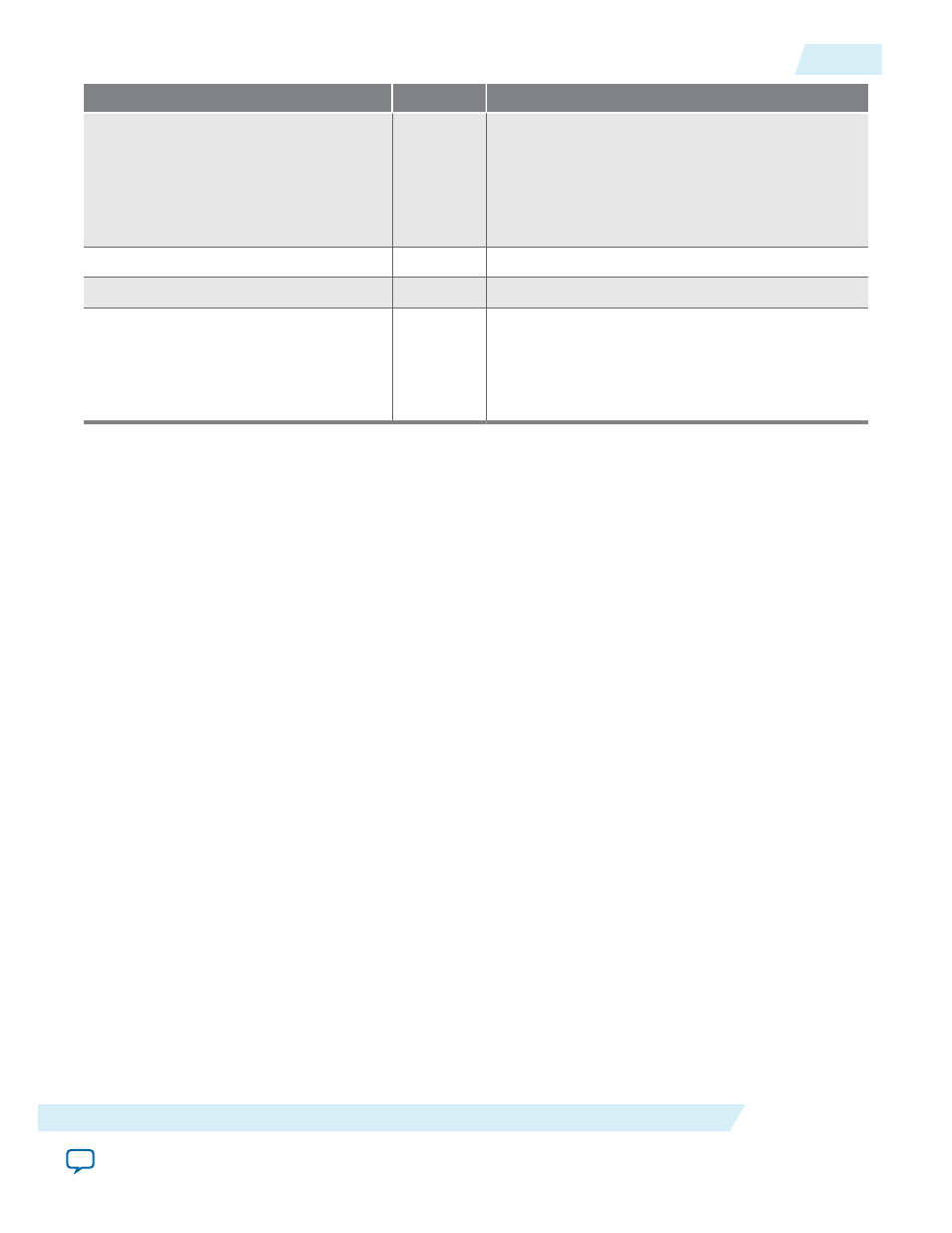

Signal Name

Direction

Description

tx_cal_busy[

Output

When asserted, indicates that the initial TX

calibration is in progress. It is also asserted if

reconfiguration controller is reset. It will not be

asserted if you manually re-trigger the calibration

IP. You must hold the channel in reset until

calibration completes.

rx_digitalreset[

Input

When asserted, resets the RX PCS.

rx_analogreset[

Input

When asserted, resets the RX CDR.

rx_cal_busy[

Output

When asserted, indicates that the initial RX

calibration is in progress. It is also asserted if

reconfiguration controller is reset. It will not be

asserted if you manually re-trigger the calibration

IP.

Related Information

•

Timing Constraints for Bonded PCS and PMA Channels

•

•

•

Register Interface and Register Descriptions

The Avalon-MM PHY management interface provides access to the Custom PHY PCS and PMA

registers, resets, error handling, and serial loopback controls. You can use an embedded controller acting

as an Avalon-MM master to send read and write commands to this Avalon-MM slave interface.

UG-01080

2015.01.19

Register Interface and Register Descriptions

9-27

Custom PHY IP Core

Altera Corporation