10gbase-r phy ip core, 10gbase-r phy ip core -1 – Altera Transceiver PHY IP Core User Manual

Page 25

10GBASE-R PHY IP Core

3

2015.01.19

UG-01080

The Altera 10GBASE-R PHY IP Core implements the functionality described in IEEE Standard 802.3

Clause 45.

It delivers serialized data to an optical module that drives optical fiber at a line rate of 10.3125 gigabits per

second (Gbps). In a multi-channel implementation of 10GBASE-R, each channel of the 10GBASE-R PHY

IP Core operates independently. Both the PCS and PMA of the 10GBASE-R PHY are implemented as

hard IP blocks in Stratix V devices, saving FPGA resources.

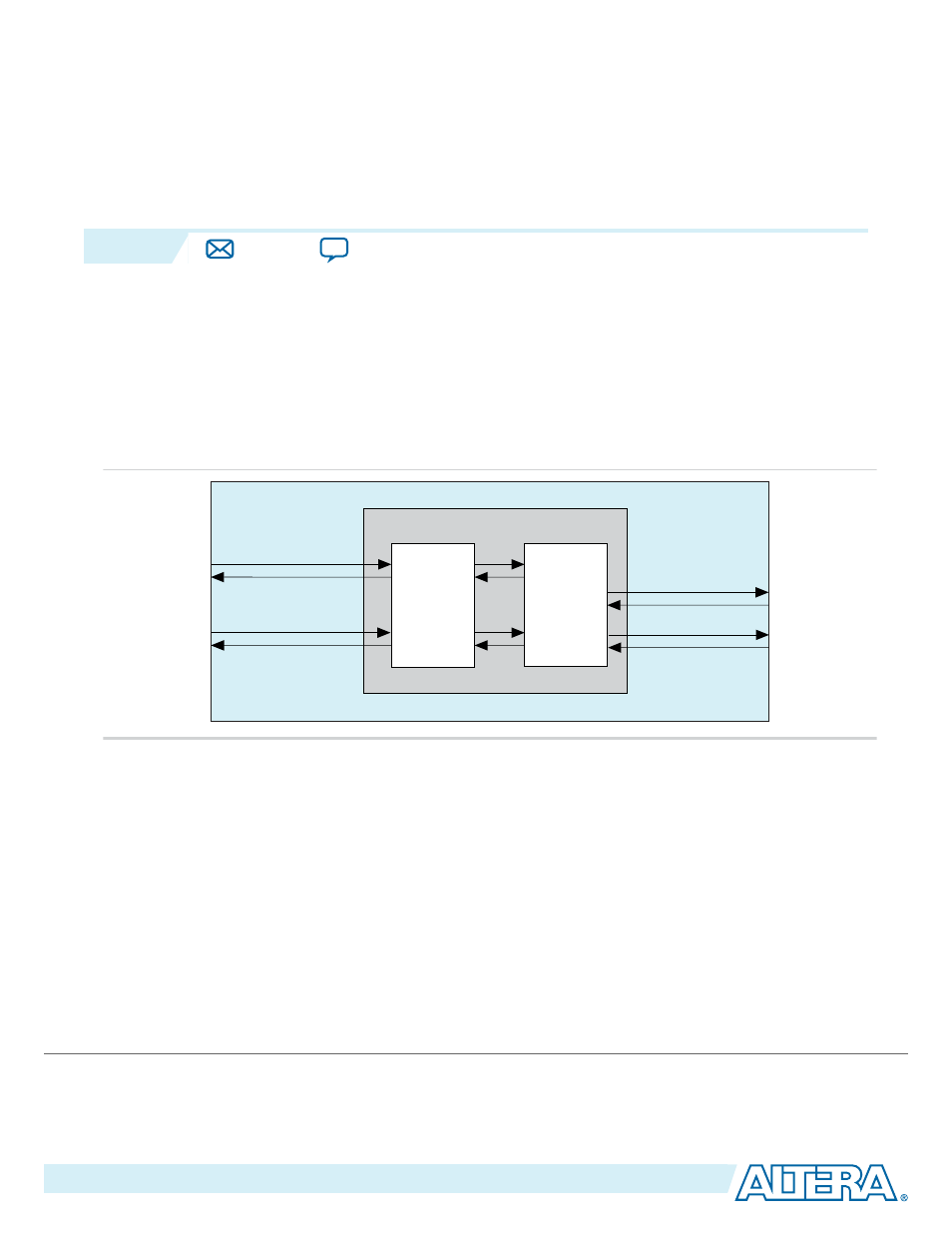

Figure 3-1: 10GBASE-R PHY with Hard PCS with PMA in Stratix V Devices

10GBASE-R PHY IP Core

10.3125 Gbps serial

XFI/SFP+

Stratix V FPGA

PMA

Hard PCS

10GBASE-R

64b/66b

Scrambler

Gearbox

SDR XGMII

72 bits @ 156.25 Mbps

Avalon-MM

Control & Status

Transceiver

Reconfiguraiton

Note: For a 10-Gbps Ethernet solution that includes both the Ethernet MAC and the 10GBASE-R PHY,

refer to the 10-Gbps Ethernet MAC MegaCore Function User Guide.

Note: For more detailed information about the 10GBASE-R transceiver channel datapath, clocking, and

channel placement, refer to the “10GBASE-R” section in the Transceiver Configurations in Stratix V

Devices chapter of the Stratix V Device Handbook.

The following figure illustrates a multiple 10 GbE channel IP core in a Stratix IV GT device. To achieve

higher bandwidths, you can instantiate multiple channels. The PCS is available in soft logic for Stratix IV

GT devices; it connects to a separately instantiated hard PMA. The PCS connects to an Ethernet MAC via

single data rate (SDR) XGMII running at 156.25 megabits per second (Mbps) and transmits data to a 10

Gbps transceiver PMA running at 10.3125 Gbps in a Stratix IV GT device.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134