Achieving deterministic latency, Achieving deterministic latency -3 – Altera Transceiver PHY IP Core User Manual

Page 271

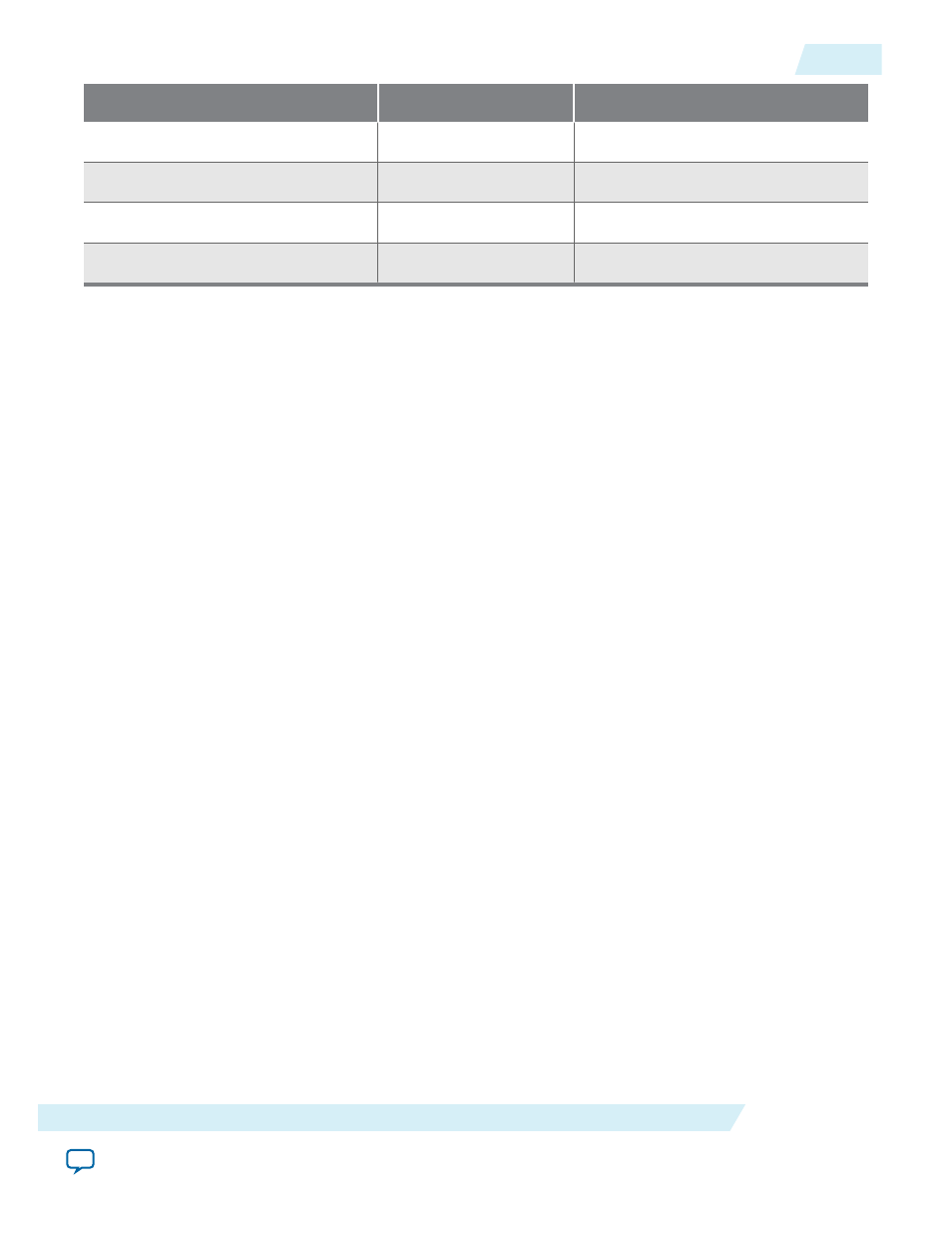

Data Rate (Mbps)

Base Data Rate (Mbps)

Clock Divider

2457.6

4915.2

2

3072.0

6144.0

2

4915.2

4915.2

1

6144.0

6144.0

1

Note: You can use PMA Direct mode in the Transceiver Native PHYs for CPRI applications that require

higher frequencies. For more information refer to the following documents:

Related Information

•

Arria V Transceiver Native PHY IP Core

•

Stratix V Transceiver Native PHY IP Core

Achieving Deterministic Latency

This section provides an overview of the calculation that help you achieve deterministic delay in the

Deterministic Latency PHY IP core.

This figure illustrates the TX and RX channels when configured as a wireless basestation communicating

to a remote radio head (RRH) using a CPRI or OBSAI interface. The figure also provides an overview of

the calculations that guarantee deterministic delay. As this figure illustrates, you can use a general-

purpose PLL to generate the clock that drives the TX CMU PLL or an external reference clock input pin.

UG-01080

2015.01.19

Achieving Deterministic Latency

11-3

Deterministic Latency PHY IP Core

Altera Corporation