Altera LVDS SERDES Transmitter / Receiver User Manual

Features

LVDS SERDES Transmitter/Receiver IP Cores User

Guide

2014.12.15

UG-MF9504

The low-voltage differential signaling serializer or deserializer (LVDS SERDES) megafunction IP cores

(ALTLVDS_TX and ALTLVDS_RX) implement the LVDS SERDES interfaces to transmit and receive

high-speed differential data. You can configure the features of these IP cores with the IP Catalog and

parameter editor.

Features

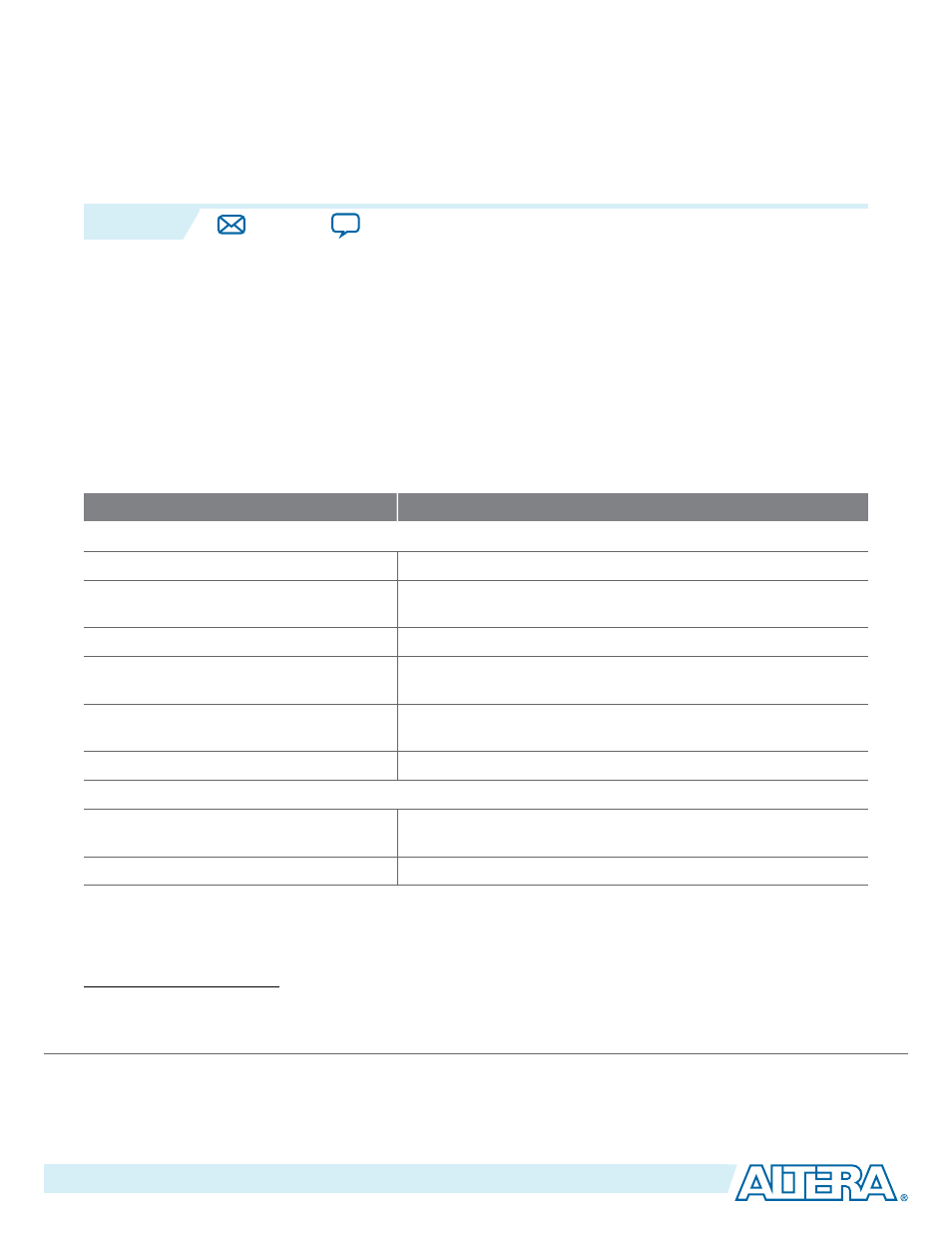

The following table lists the features of the ALTLVDS_TX and ALTLVDS_RX IP cores.

Table 1: ALTLVDS_TX and ALTLVDS_RX Features

Features

Supported devices

ALTLVDS_TX and ALTLVDS_RX

Parameterizable data channel widths

All Arria

®

, Cyclone

®

, and Stratix

®

series devices.

Parameterizable serializer/deserializer

(SERDES) factors

All Arria, Cyclone, and Stratix series devices.

Registered input and output ports

All Arria, Cyclone, and Stratix series devices.

Support for external phase-locked loops

(PLL)

All Arria, Cyclone, and Stratix series devices.

PLLs sharing between transmitters and

receivers

All Arria, Cyclone, and Stratix series devices.

PLL control signals

All Arria, Cyclone, and Stratix series devices.

ALTLVDS_RX Only

Dynamic phase alignment (DPA) mode

support

All Arria and Stratix

(1)

devices.

DPA PLL calibration support

All Stratix

(1)

series devices.

(1)

DPA is available starting from Stratix GX onwards. The first generation Stratix device family does not

support DPA.

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134

Document Outline

- LVDS SERDES Transmitter/Receiver IP Cores User Guide

- Features

- Installing and Licensing IP Cores

- Customizing and Generating IP Cores

- Upgrading IP Cores

- Parameter Settings

- Ports

- Prototypes and Component Declarations

- Functional Description

- Receiver Modes

- DPA PLL Calibration

- Initialization and Reset

- Source-Synchronous Timing Analysis and Timing Constraints

- Arria II GX, Arria V, Arria V GZ, Cyclone V, and Stratix V LVDS Package Skew Compensation Report Panel

- ALTLVDS IP Core in External PLL Mode

- Simulating Altera IP Cores in other EDA Tools

- Generating ALTLVDS IP Core Using Clear Box Generator

- Document Revision History