Altera Transceiver PHY IP Core User Manual

Page 659

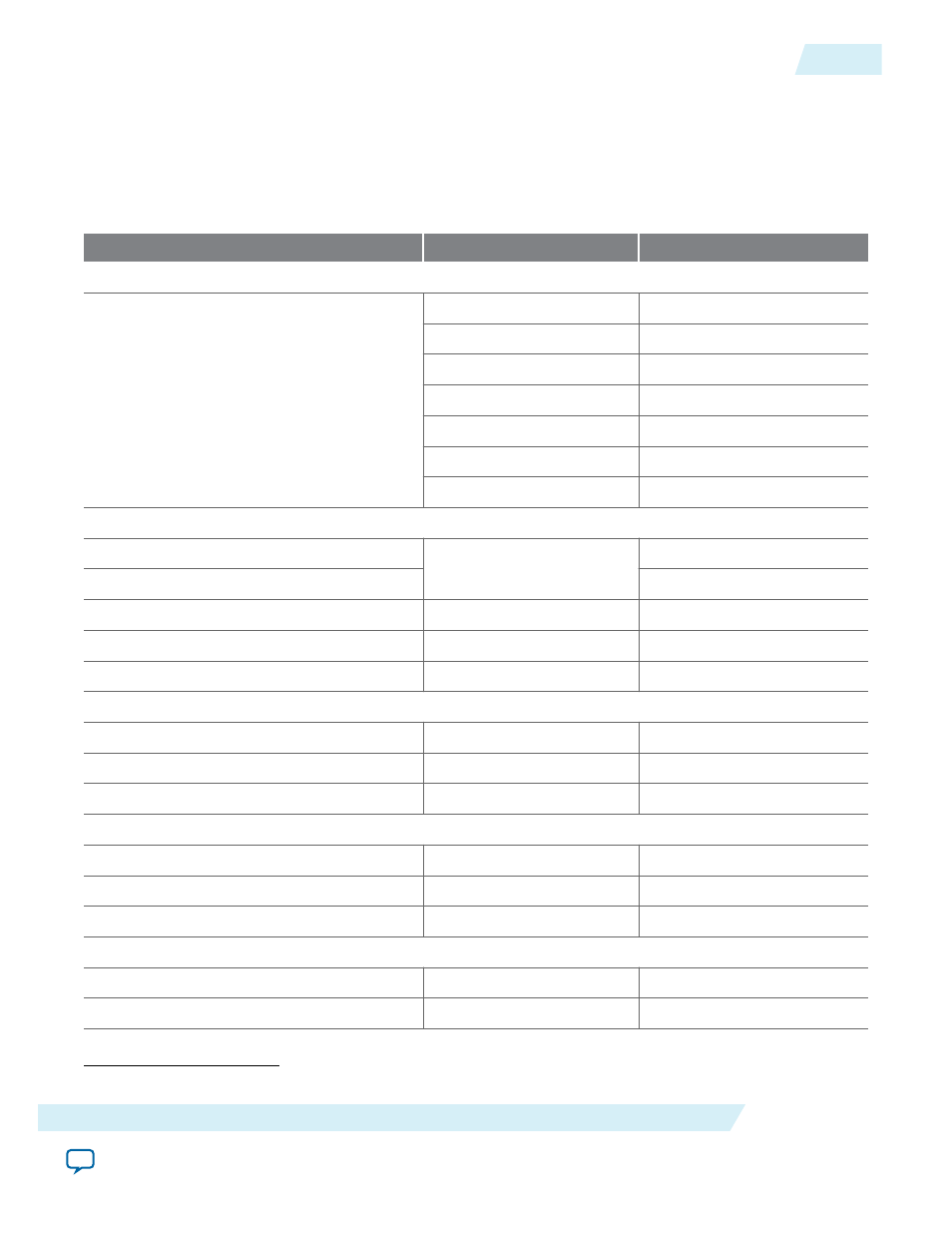

Differences Between Custom PHY Ports in Stratix IV and Stratix V Devices

This section lists the differences between the top-level signals in Stratix IV GX and Stratix V GX/GS

devices.

Table 20-7: Custom PHY Correspondences between Stratix IV GX Device and Stratix V Device Signals

ALTGX

(23)

Custom PHY

Width

Avalon-MM Management Interface

Not available

phy_mgmt_clk_reset

1

phy_mgmt_clk

1

phy_mgmt_address

8

phy_mgmt_read

1

phy_mgmt_readdata

32

phy_mgmt_write

1

phy_mgmt_writedata

32

Clocks

cal_blk_clk

These signals are included in

the

reconfig_to_xcvr

bus

—

reconfig_clk

—

pll_inclk

pll_ref_clk

[<p>-1:0]

rx_coreclk

rx_coreclkin

—

tx_coreclk

tx_coreclkin

—

Avalon-ST TX Interface

tx_datain

tx_parallel_data

[<d><n>-1:0]

tx_ctrlenable

tx_datak

[<d><n>-1:0]

rx_ctrldetect

rx_datak

[<d><n>-1:0]

Avalon-ST RX Interface

rx_dataout

rx_parallel_data

[<d><n>-1:0]

rx_runningdisp

rx_runningdisp

[<d/8><n>-1:0]

rx_enabyteord

rx_enabyteord

[<n>-1:0]

High Speed Serial I/O

rx_datain

rx_serial_data

[<n>-1:0]

tx_dataout

tx_serial_data

[<n>-1:0]

(23)

<n> = the number of lanes. <d> = the total deserialization factor from the pin to the FPGA fabric.

UG-01080

2013.12.20

Differences Between Custom PHY Ports in Stratix IV and Stratix V Devices

20-13

Migrating from Stratix IV to Stratix V Devices Overview

Altera Corporation