Turning on dfe continuous adaptive mode, Turning on dfe continuous adaptive mode -22 – Altera Transceiver PHY IP Core User Manual

Page 539

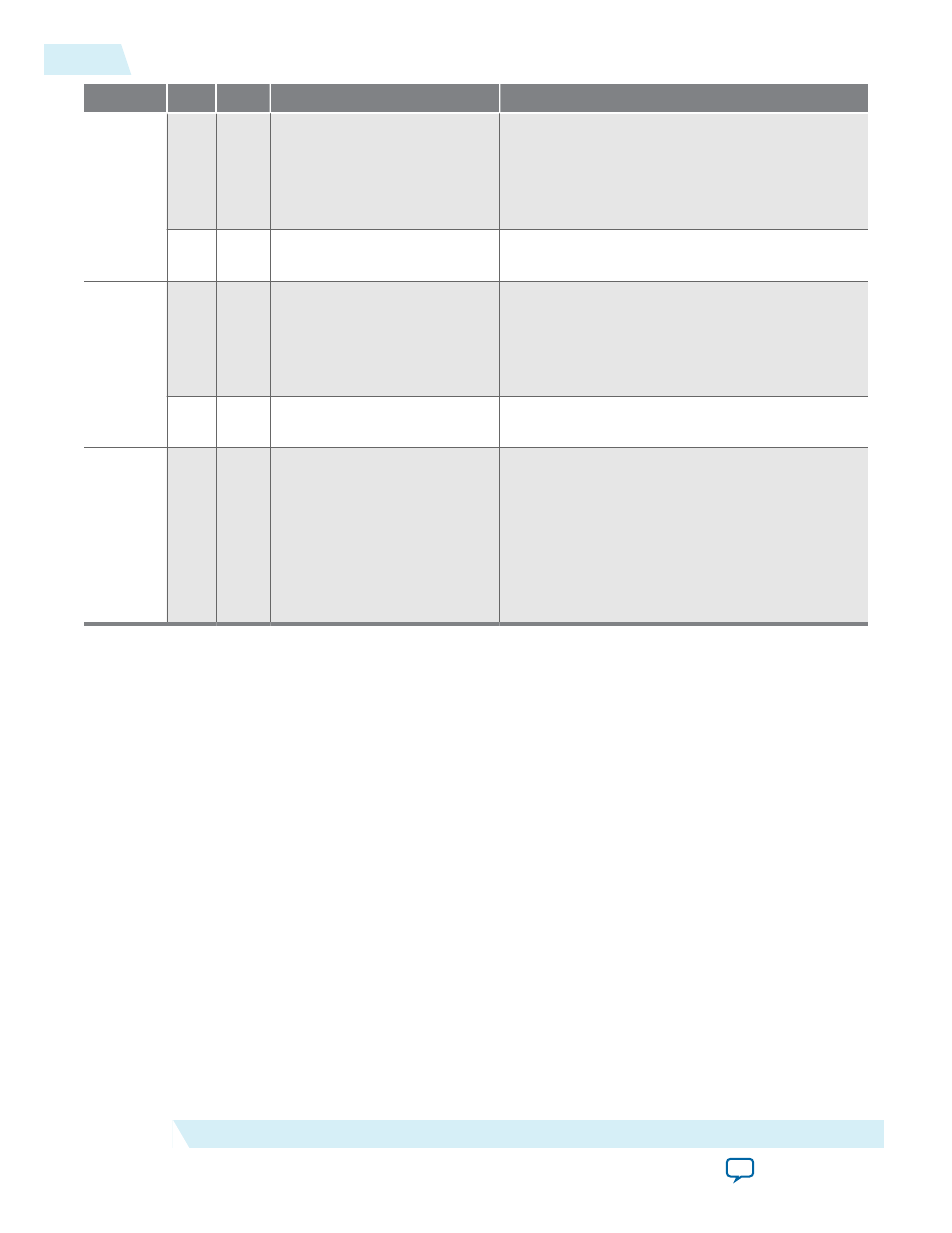

Offset

Bits

R/W

Register Name

Description

0x4

[3]

RW

tap 4 polarity

Specifies the polarity of the fourth post tap as

follows:

• 0: negative polarity

• 1: positive polarity

[2:0] RW

tap 4

Specifies the coefficient for the fourth post tap.

The valid range is 0–7.

0x5

[3]

RW

tap 5 polarity

Specifies the polarity of the fifth post tap as

follows:

• 0: negative polarity

• 1: positive polarity

[2:0] RW

tap 5

Specifies the coefficient for the fifth post tap.

The valid range is 0–3.

0xB

[0]

RW

DFE_adaptation

Writing a 0 or 1 to this bit turns on the DFE

power and initiates triggered DFE mode for the

specified channel. Ensure busy bit is 0 to

complete the reconfiguration process. Reading

(0xB) register bit as 1 and busy bit as 0, indicates

that the DFE is in triggered mode. To turn off

the triggered DFE mode, write 0 to bit 1 of

register 0x0.

Controlling DFE Using Register-Based Reconfiguration

In register-based mode, you use a sequence of Avalon-MM reads and writes to configure the DFE and to

turn it on and off. There are three ways to control the DFE using a sequence of register-based

reconfiguration reads and writes.

Turning on DFE Continuous Adaptive mode

Complete the following steps to turn on DFE continuous adaptive mode:

1. Read the DFE control and status register busy bit (bit 8) until it is clear.

2. Write the logical channel number of the channel to be updated to the DFE logical channel number

register.

3. Write the

DFE_offset

address to 0x0.

4. Write the data value 2'b11 to the data register. This data powers on DFE and enables the DFE

continuous adaptation engine.

5. Write the

control and status

register write bit to 1'b1.

6. Read the

control and status

register

busy

bit. Continue to read the

busy

bit while its value is 1b’1.

7. When busy = 1’b0, the Transceiver Reconfiguration Controller has updated the logical channel

specified in Step 2 with the data specified in Steps 3 and 4.

16-22

Controlling DFE Using Register-Based Reconfiguration

UG-01080

2015.01.19

Altera Corporation

Transceiver Reconfiguration Controller IP Core Overview