Additional options parameters, Additional options parameters -7 – Altera Transceiver PHY IP Core User Manual

Page 254

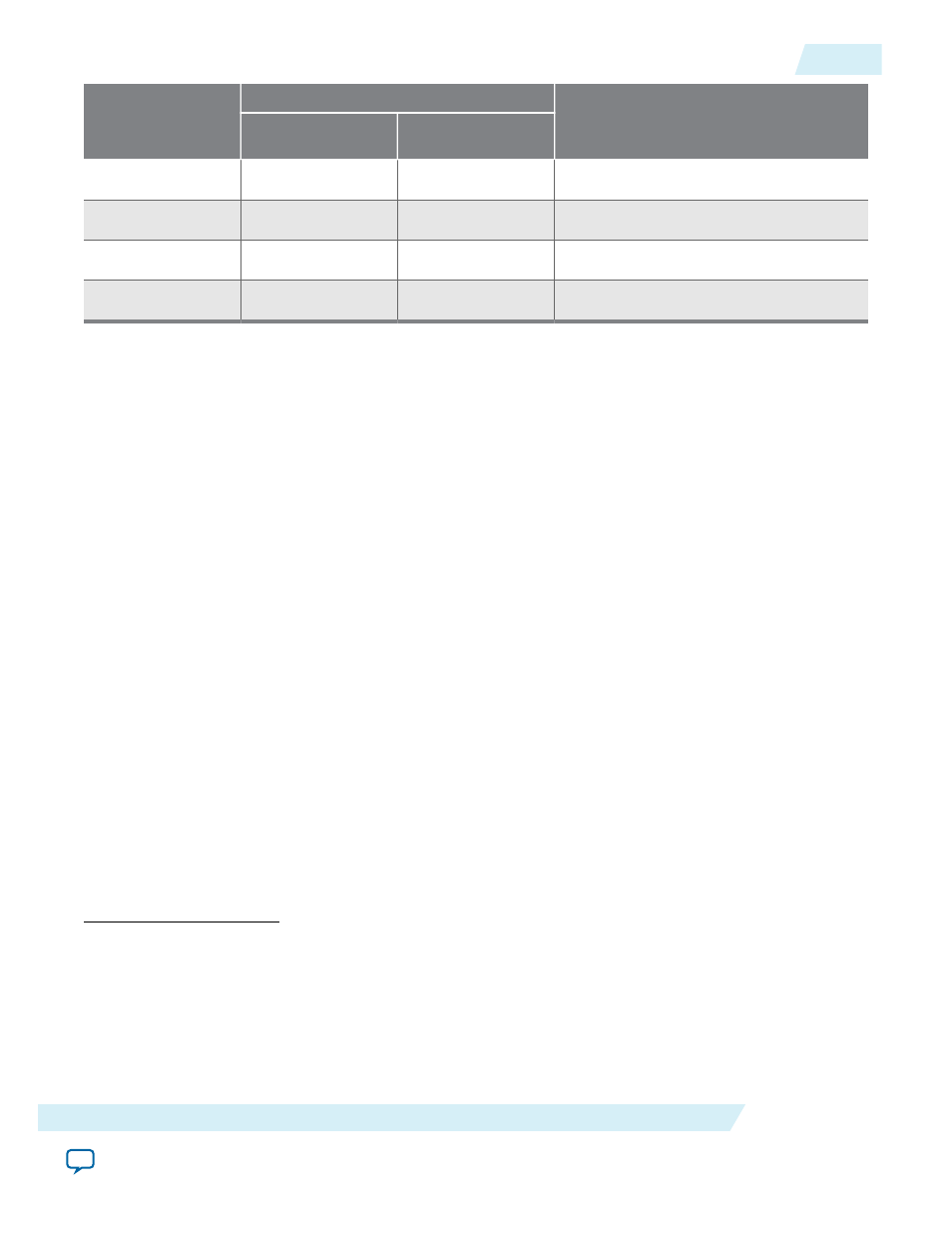

FPGA Fabric -

Transceiver Interface

Width

PCS-PMA Interface Width

tx_clkout and rx_clkout frequency

Standard Datapath

10G Datapath

50

—

40

data rate/50

(6)

64

—

32

data rate/32

(7)

64

—

64

data rate/64

66

—

40

data rate/66

Related Information

•

•

Additional Options Parameters

The parameters on the Additional Options tab control clocking and datapath options. Both bonded (×N)

and non-bonded modes are available. In bonded modes, a single PLL can drive all channels. In non-

bonded modes, each channel may have its own PLL.

(6)

For this datapath configuration, the

tx_clkout

frequency generated by the Low Latency PHY is the data

rate /40. You must generate a /50 frequency clock from the /40 clock and feed this clock back into the

tx_

coreclkin

. The

rx_clkout

frequency generated by the Low Latency PHY is /40 of the data rate. You must

generate a /50 frequency from the recovered clock and feed this back into the

rx_coreclkin

.

(7)

For this datapath configuration, the

tx_clkout

frequency generated by the Low Latency PHY is the data

rate/32. You must generate a /64 frequency clock from the /32 clock and feed this clock back into the

tx_

coreclkin

. The

rx_clkout

frequency generated by the Low Latency PHY is the data rate/32. You must

generate a /64 frequency from the recovered clock and feed this back into the

rx_coreclkin

UG-01080

2015.01.19

Additional Options Parameters

10-7

Low Latency PHY IP Core

Altera Corporation