3 global mode entry (gmode), Figure 30-23. global mode entry (gmode), Table 30-14. gmode field descriptions (continued) – Freescale Semiconductor MPC8260 User Manual

Page 960: Global mode entry (gmode) -40, Gmode field descriptions -40, Section 30.10.1.3, “global mode entry, Gmode)

ATM Controller and AAL0, AAL1, and AAL5

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

30-40

Freescale Semiconductor

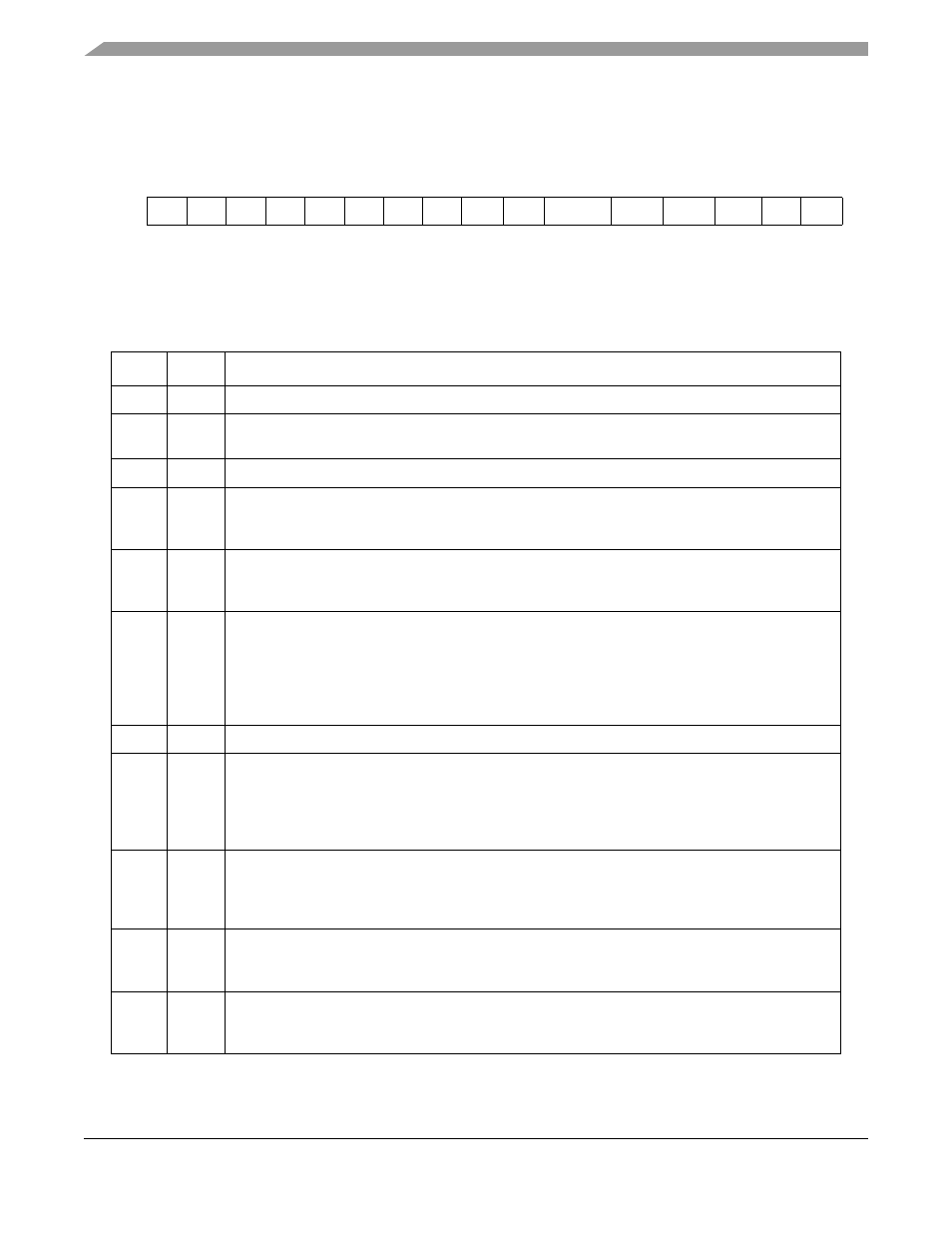

30.10.1.3 Global Mode Entry (GMODE)

shows the layout of the global mode entry (GMODE).

describes GMODE fields.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

0

0

GBL

0

0

0

ALB CTB REM

0

IMA_EN

1

1

MPC8264 and MPC8266 only.

UEAD

CUAB EVPT

0

ALM

Figure 30-23. Global Mode Entry (GMODE)

Table 30-14. GMODE Field Descriptions

Bits

Name

Description

0–1

—

Reserved, should be cleared.

2

GBL

Global. Asserting GBL enables snooping of connection tables. GBL should not be asserted if any of

the related DMAs will access the local bus.

3–5

—

Reserved, should be cleared.

6

ALB

Address look up bus for CAM or address compression tables

0 Reside on the 60x bus.

1 Reside on the local bus.

7

CTB

External connection tables bus

0 Reside on the 60x bus.

1 Reside on the local bus.

8

REM

1

Receive emergency mode

0 Enable REM operation. When the receive FIFO is full, the ATM transmitter stops sending data

cells until the receiver emergency state is cleared (FIFO not full). The transmitter pace is

maintained, although a small CDV may be introduced. This mode enables the receiver to receive

bursts of cells above the steady state performance.

1 Disable REM operation. Note that to check system performance the user may want to set this bit.

9–10

—

Reserved, should be cleared.

10

IMA_E

N

MPC8264 and MPC8266 only: Enable the associated FCC in IMA mode.

0 Default. FCC Enabled in normal ATM mode

1 FCC enabled in IMA mode

Note that individual PHYs of those IMA-mode enabled FCCs may still be set for non-IMA

functionality via the IMAPHY register in the IMA root table.

11

UEAD

User-defined cells extended address mode. See

Section 30.7.1, “UDC Extended Address Mode

.”

0 Disable UEAD mode.

1 Enable UEAD mode.

12

CUAB

Check unallocated bits

0 Do not check unallocated bits during address compression.

1 Check unallocated bits during address compression.

13

EVPT

External address compression VP table

0 VP table resides in dual-port RAM.

1 VP table reside in external memory.