3 atm event register (fcce)/mask register (fccm), Atm event register (fcce)/mask register (fccm) -90 – Freescale Semiconductor MPC8260 User Manual

Page 1010

ATM Controller and AAL0, AAL1, and AAL5

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

30-90

Freescale Semiconductor

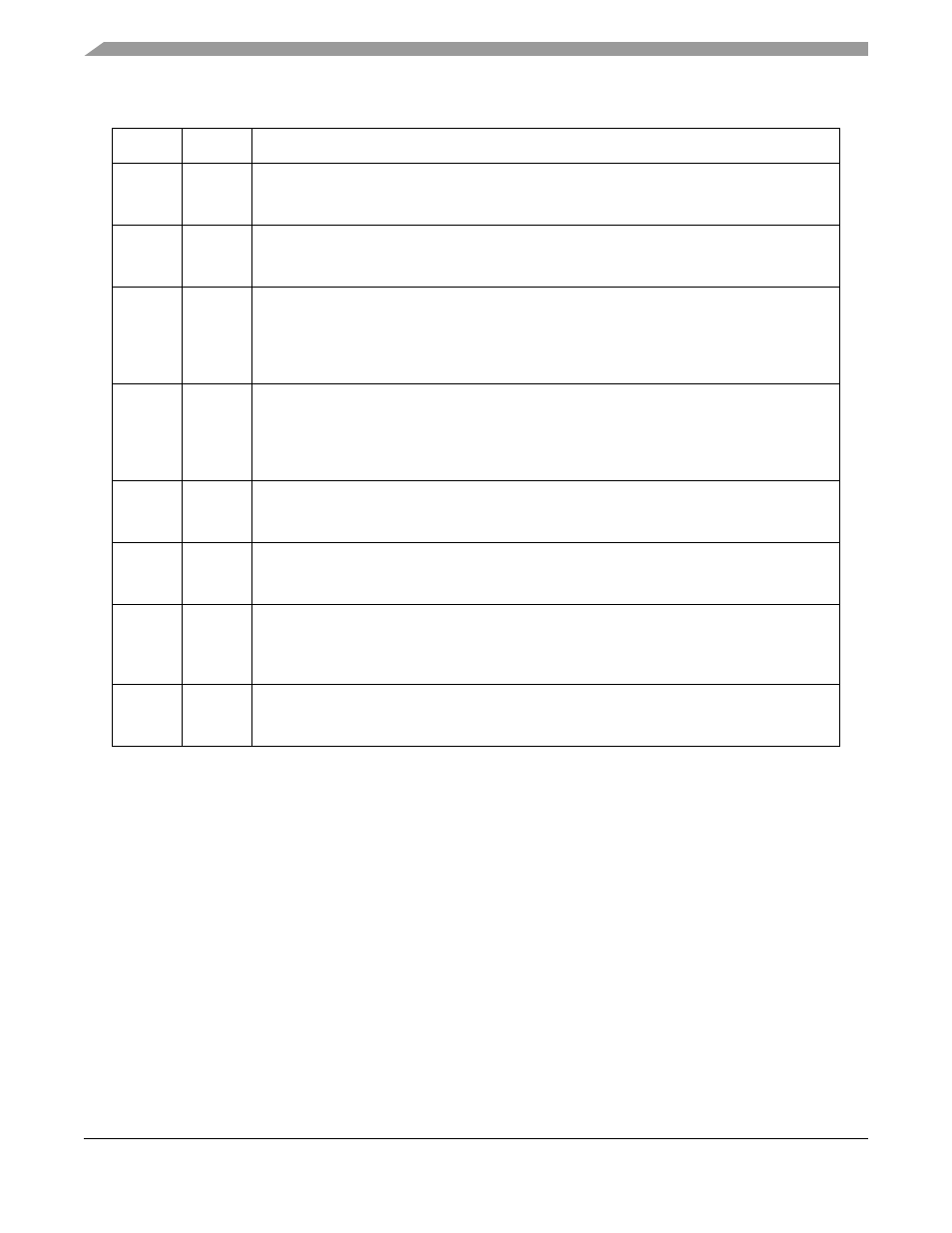

30.13.3 ATM Event Register (FCCE)/Mask Register (FCCM)

The FCCE register is the ATM controller event register when the FCC operates in ATM mode. When it

recognizes an event, the ATM controller sets the corresponding FCCE bit. Interrupts generated by this

register can be masked in FCCM. FCCE is memory-mapped and can be read at any time. Bits are cleared

by writing ones to them; writing zeros has no effect. Unmasked bits must be cleared before the CP clears

the internal interrupt request.

FCCM is the ATM controller mask register. The FCCM has the same bit format as FCCE. Setting an

FCCM bit enables and clearing a bit masks the corresponding interrupt in the FCCE.

24

TSIZE

Transmit UTOPIA data bus size

0 UTOPIA 8-bit data bus size

1 UTOPIA 16-bit data bus size

25

RSIZE

Receive UTOPIA data bus size

0 UTOPIA 8-bit data bus size

1 UTOPIA 16-bit data bus size

26

UPRM

UTOPIA priority mode.

0 Round robin. Polling is done from PHY zero to the PHY specified in LAST PHY. When a PHY

is selected, the UTOPIA interface continues to poll the next PHY in order.

1 Fixed priority. Polling is done from PHY zero to the PHY specified in LAST PHY. When a PHY

is selected, the UTOPIA interface continues to poll from PHY zero.

27

UPLM

UTOPIA polling mode.

0 Single Clav polling. Polling is done using Add[4–0] and Clav. Selection is done using

Add[4–0]. Up to 31 PHYs can be polled.

1 Direct polling. Polling is done using Clav[3–0]. Selection is done using Add[1–0]. Up to 4

PHYs can be polled.

28

RUMP

Receive UTOPIA multiple PHY mode.

0 Receive UTOPIA single PHY mode is selected

1 Receive UTOPIA multiple PHY mode is selected (Use this mode for IMA support

1

)

29

HECI

HEC included. Used in UDC mode only.

0 HEC octet is not included when UDC mode is enabled.

1 HEC octet is included when UDC mode is enabled.

30

HECC

Receive HEC check

0 Do not check Rx HEC

1 Check Rx HEC. HEC errors are reported in UTOPIAE counter (see

”). This option can be used only in UTIPIA 8-bit data bus size.

31

COS

Coset mode enable

0 Check Rx HEC with no COSET

1 Check Rx HEC with COSET mode enabled

1

MPC8264 and MPC8266 only.

Table 30-47. FCC ATM Mode Register (FPSMR) (continued)

Bits

Name Description