1 scc base addresses, Scc base addresses -14, Section 20.3.1, “scc – Freescale Semiconductor MPC8260 User Manual

Page 692: Base addresses

Serial Communications Controllers (SCCs)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

20-14

Freescale Semiconductor

20.3.1

SCC Base Addresses

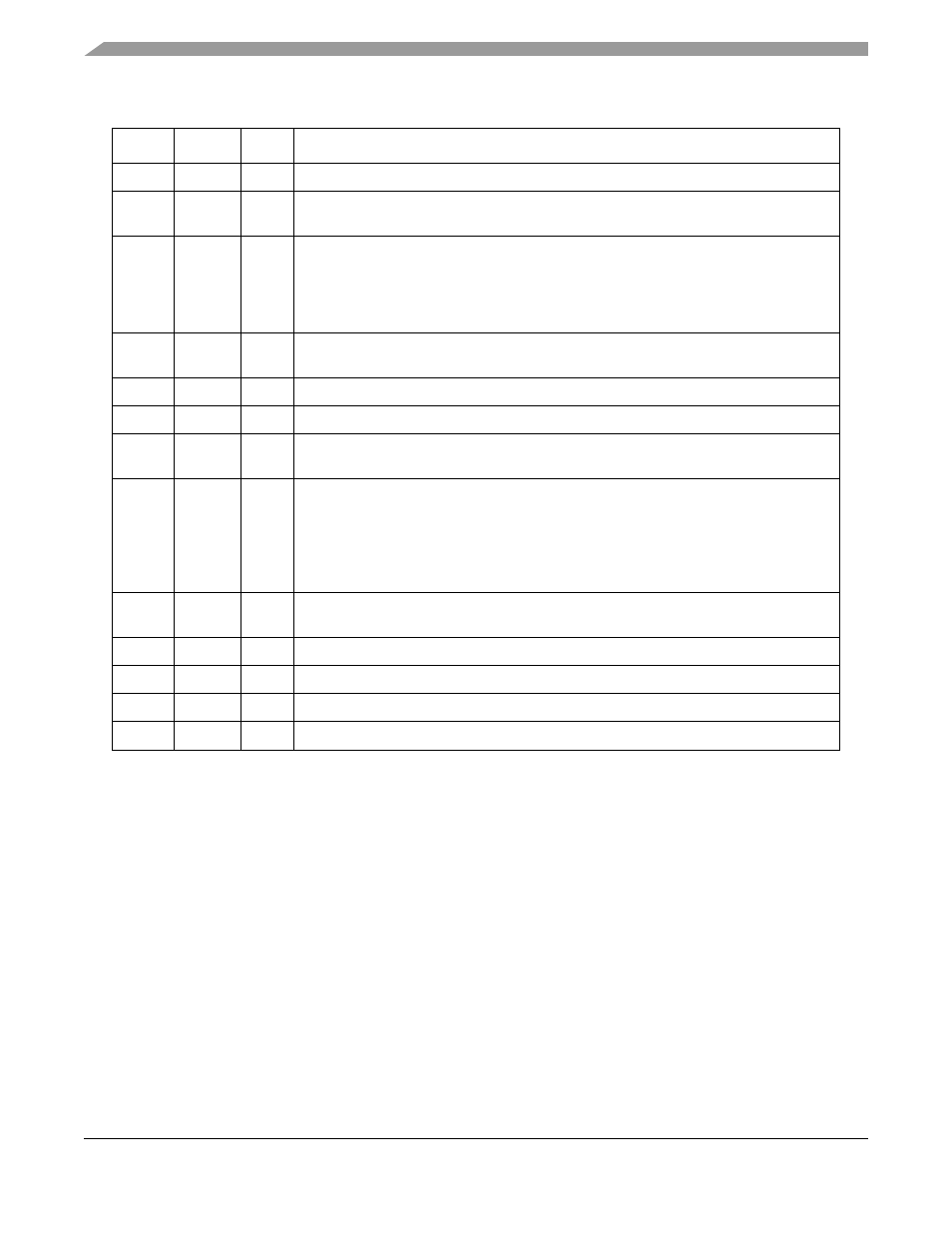

The CPM maintains a section of RAM called the parameter RAM, which contains many parameters for

the operation of the FCCs, SCCs, SMCs, SPI, I

2

C, and IDMA channels. SCC base addresses are described

The exact definition of the parameter RAM is contained in each protocol subsection describing a device

that uses a parameter RAM. For example, the Ethernet parameter RAM is defined differently in some

locations from the HDLC-specific parameter RAM.

0x08

RSTATE

Word

Rx internal state

3

0x0C

Word

Rx internal buffer pointer

2

. The Rx and Tx internal buffer pointers are updated by the

SDMA channels to show the next address in the buffer to be accessed.

0x10

RBPTR

Hword

Current RxBD pointer. Points to the current BD being processed or to the next BD the

receiver uses when it is idling. After reset or when the end of the BD table is reached,

the CPM initializes RBPTR to the value in the RBASE. Although most applications do

not need to write RBPTR, it can be modified when the receiver is disabled or when no

Rx buffer is in use.

0x12

Hword

Rx internal byte count

2

. The Rx internal byte count is a down-count value initialized with

MRBLR and decremented with each byte written by the supporting SDMA channel.

0x14

Word

Rx temp

3

0x18

TSTATE

Word

Tx internal state

3

0x1C

Word

Tx internal buffer pointer

2

. The Rx and Tx internal buffer pointers are updated by the

SDMA channels to show the next address in the buffer to be accessed.

0x20

TBPTR

Hword

Current TxBD pointer. Points to the current BD being processed or to the next BD the

transmitter uses when it is idling. After reset or when the end of the BD table is reached,

the CPM initializes TBPTR to the value in the TBASE. Although most applications do not

need to write TBPTR, it can be modified when the transmitter is disabled or when no Tx

buffer is in use (after a

STOP

TRANSMIT

or

GRACEFUL

STOP

TRANSMIT

command is issued

and the frame completes its transmission).

0x22

Hword

Tx internal byte count

2

. A down-count value initialized with TxBD[Data Length] and

decremented with each byte read by the supporting SDMA channel.

0x24

Word

Tx temp

3

0x28

RCRC

Word

Temp receive CRC

2

0x2C

TCRC

Word

Temp transmit CRC

2

0x30

Protocol-specific area. (The size of this area depends on the protocol chosen.)

1

From SCC base. See

Section 20.3.1, “SCC Base Addresses

.”

2

These parameters need not be accessed for normal operation but may be helpful for debugging.

3

For CP use only

Table 20-4. SCC Parameter RAM Map for All Protocols (continued)

Offset

1

Name

Width

Description