Freescale Semiconductor MPC8260 User Manual

Page 255

External Signals

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

6-15

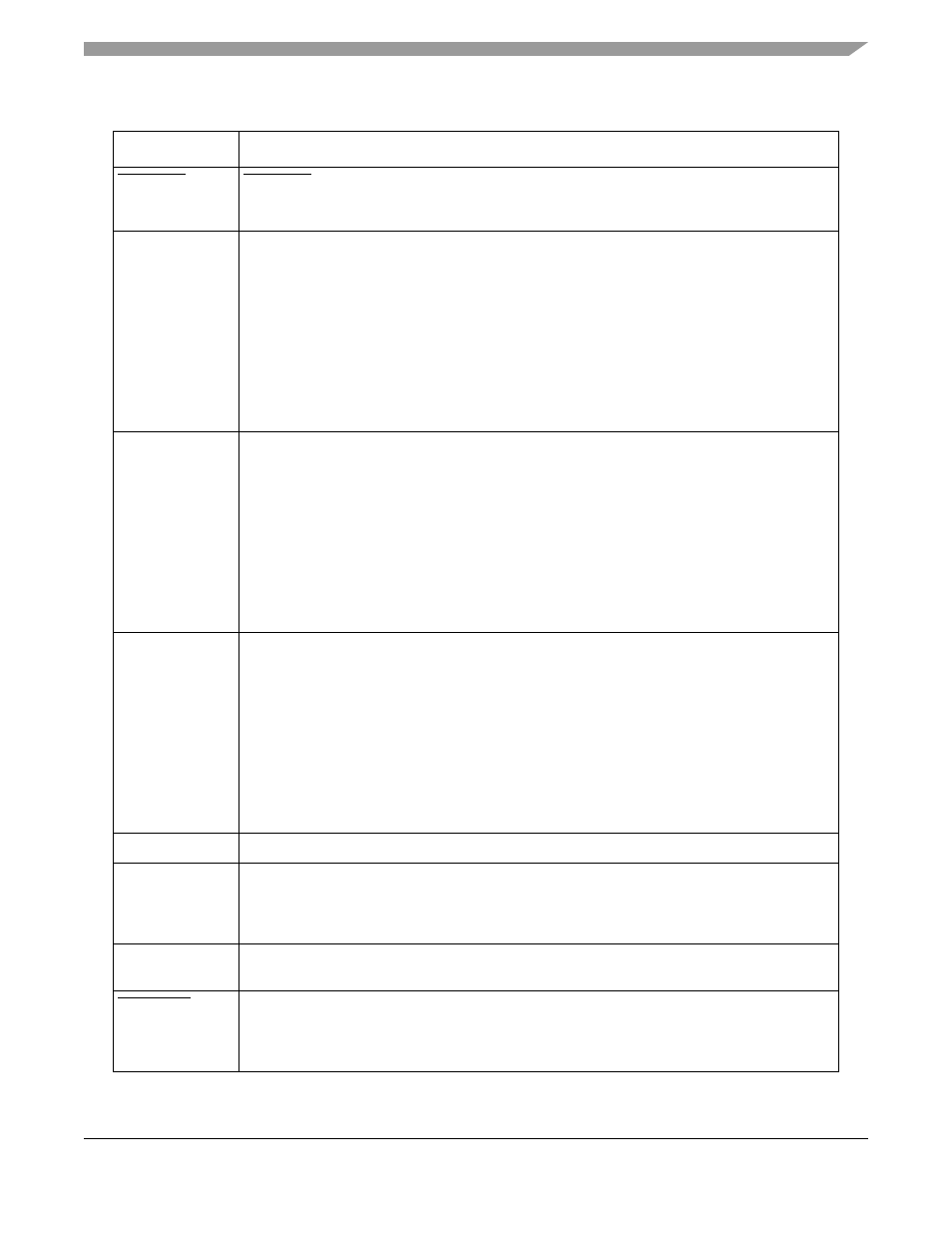

RSTCONF

RSTCONF —Input used during reset configuration sequence of the chip. Find detailed

explanation of its function in

Section 5.1.2, “Power-On Reset Flow,”

and

MODCK1

AP[1]

TC[0]

BNKSEL[0]

MODCK1—Clock mode input. Defines the operating mode of internal clock circuits.

Address parity 1—(Input/output) The 60x master that drives the address bus, drives also the

address parity signals. The value driven on address parity 1 pin should give odd parity (odd

number of 1s) on the group of signals that includes address parity 1 and A[8–15].

Transfer Code 0—The transfer code output pins supply information that can be useful for debug

purposes for each of the PowerQUICC II’s initiated bus transactions.

Bank Select 0—The bank select outputs are used for selecting SDRAM bank when the

PowerQUICC II is in 60x compatible bus mode. BNKSEL0 is msb of the three BNKSEL signals.

MODCK2

AP[2]

TC[1]

BNKSEL[1]

MODCK2—Clock mode input. Defines the operating mode of internal clock circuits.

Address parity 2—(Input/output) The 60x master that drives the address bus, drives also the

address parity signals. The value driven on address parity 2 pin should give odd parity (odd

number of 1s) on the group of signals that includes address parity 2 and A[16–23].

Transfer code 1—The transfer code output pins supply information that can be useful for debug

purposes for each of the PowerQUICC II’s initiated bus transactions.

Bank select 1—The bank select outputs are used for selecting SDRAM bank when the

PowerQUICC II is in 60x-compatible bus mode.

MODCK3

AP[3]

TC[2]

BNKSEL[2]

MODCK3—Clock mode input. Defines the operating mode of internal clock circuits.

Address parity 3—(Input/output) The 60x master that drives the address bus, drives also the

address parity signals. The value driven on address parity 3 pin should give odd parity (odd

number of 1s) on the group of signals that includes address parity 3 and A[24—31].

Transfer code 2—The transfer code output pins supply information that can be useful for debug

purposes for each of the PowerQUICC II’s initiated bus transactions.

Bank select 2—The bank select outputs are used for selecting SDRAM bank when the

PowerQUICC II is in 60x-compatible bus mode. BNKSEL2 is lsb of the three BNKSEL signals.

XFC

External filter capacitance—Input connection for an external capacitor filter for PLL circuitry.

CLKIN1

Clock In—Primary clock input to PowerQUICC II’s PLL. In a PCI system

1

, where the

PowerQUICC II PCI interface is operated from the PCI bus clock, CLKIN should be connected to

the PCI bus clock. In that case, the 60x bus clock is driven on CLKOUT. See

and

CLKIN2

1

Clock In2—This is the clock input to the PowerQUICC II’s DLL, which is used for deskewing the

output reference clock. See

and

.

PCI_MODE

1

PCI mode pin—This pin enables the PCI bridge of the PowerQUICC II.

• When Low, the PCI bridge is enabled, PCI interface replaces the Local bus.

• When High, the PCI bridge is disabled, the PowerQUICC II operates with the Local bus.

This pin has an internal pull up resistor so it defaults to Local bus operation.

Table 6-1. External Signals (continued)

Signal Description