Freescale Semiconductor MPC8260 User Manual

Page 153

Memory Map

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

3-7

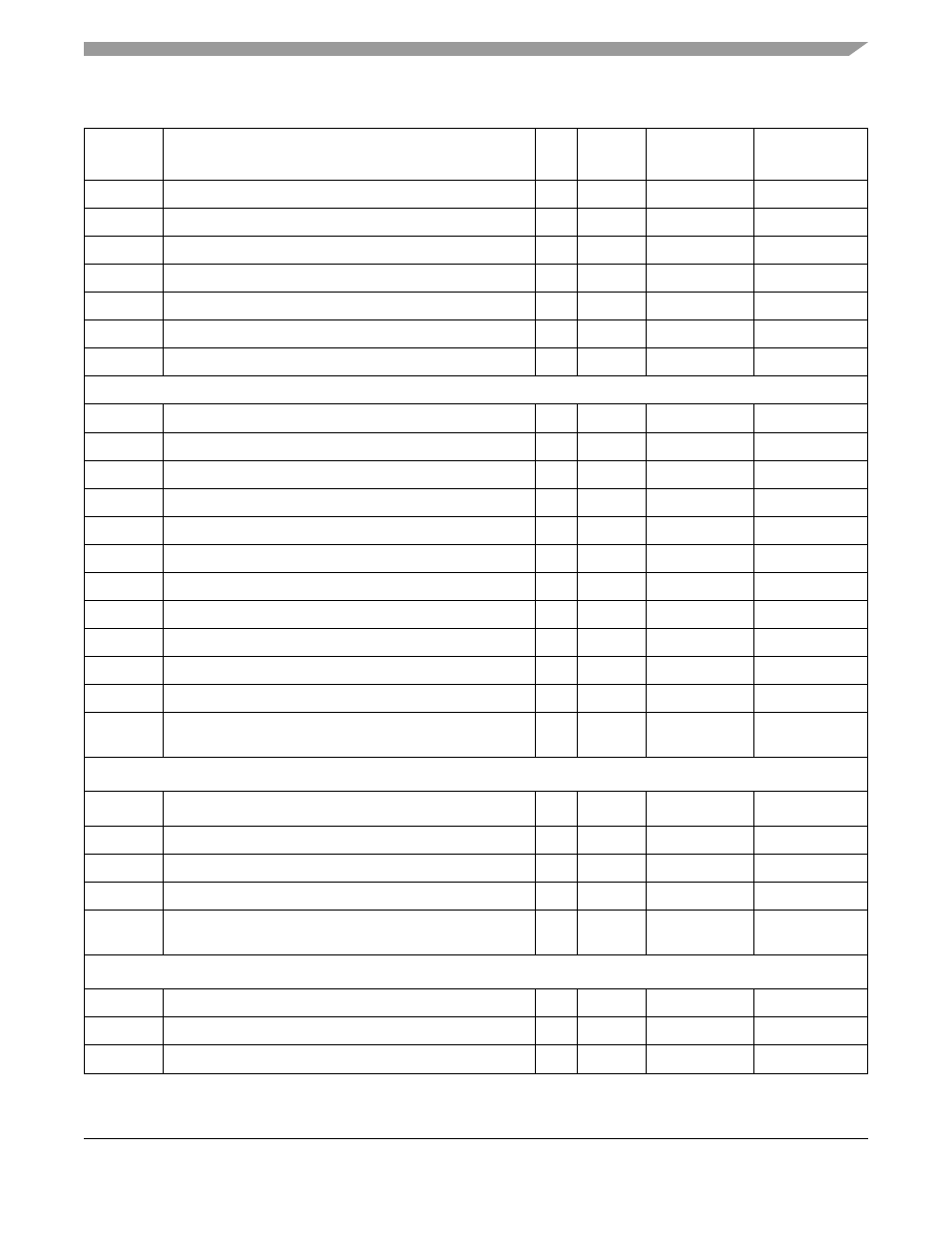

0x108E0

PCI inbound comparison mask register 1 (PICMR1)

2

R/W

32 bits

0x0000_0000

0x108E8

PCI inbound translation address register 0 (PITAR0)

2

R/W

32 bits

0x0000_0000

0x108F0

PCI inbound base address register 0 (PIBAR0)

2

R/W

32 bits

0x0000_0000

0x108F8

PCI inbound comparison mask register 0 (PICMR0)

2

R/W

32 bits

0x0000_0000

0x10900

PCI CFG_ADDR

2

R/W

32 bits

undefined

0x10904

PCI CFG_DATA

2

R/W

32 bits

0x0000_0000

0x10908

PCI INT_ACK

2

R/W

32 bits

undefined

Interrupt Controller

0x10C00

SIU interrupt configuration register (SICR)

R/W

16 bits

0x0000

0x10C02

Reserved

—

16 bits

—

—

0x10C04

SIU interrupt vector register (SIVEC)

R/W

32 bits

0x0000_0000

0x10C08

SIU interrupt pending register (high) (SIPNR_H)

R/W

32 bits

undefined

0x10C0C

SIU interrupt pending register (low) (SIPNR_L)

R/W

32 bits

0x0000_0000

0x10C10

SIU interrupt priority register (SIPRR)

R/W

32 bits

0x0530_9770

0x10C14

CPM interrupt priority register (high) (SCPRR_H)

R/W

32 bits

0x0530_9770

0x10C18

CPM interrupt priority register (low) (SCPRR_L)

R/W

32 bits

0x0530_9770

0x10C1C

SIU interrupt mask register (high) (SIMR_H)

R/W

32 bits

0x0000_0000

0x10C20

SIU interrupt mask register (low) (SIMR_L)

R/W

32 bits

0x0000_0000

0x10C24

SIU external interrupt control register (SIEXR)

R/W

32 bits

0x0000_0000

0x10C28–

0x10C7F

Reserved

—

88 bytes

—

—

Clocks and Reset

0x10C80

System clock control register (SCCR)

R/W

32 bits

0x10C88

System clock mode register (SCMR)

R

32 bits

see

0x10C90

Reset status register (RSR)

R/W

32 bits

0x0000_0003

0x10C94

Reset mode register (RMR)

R/W

32 bits

0x0000_0000

0x10C98–

0x10CFF

Reserved

—

104

bytes

—

—

Input/Output Port

0x10D00

Port A data direction register (PDIRA)

R/W

32 bits

0x0000_0000

0x10D04

Port A pin assignment register (PPARA)

R/W

32 bits

0x0000_0000

0x10D08

Port A special options register (PSORA)

R/W

32 bits

0x0000_0000

Table 3-1. Internal Memory Map (continued)

Address

(offset)

Register

R/W

Size

Reset

Section/Page