24 pci hot swap register block, Figure 9-56. hot swap register block, Pci hot swap register block -60 – Freescale Semiconductor MPC8260 User Manual

Page 366: Hot swap register block -60, Table 9-42

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

9-60

Freescale Semiconductor

Table 9-42. describes the PCI bus arbiter configuration register fields.

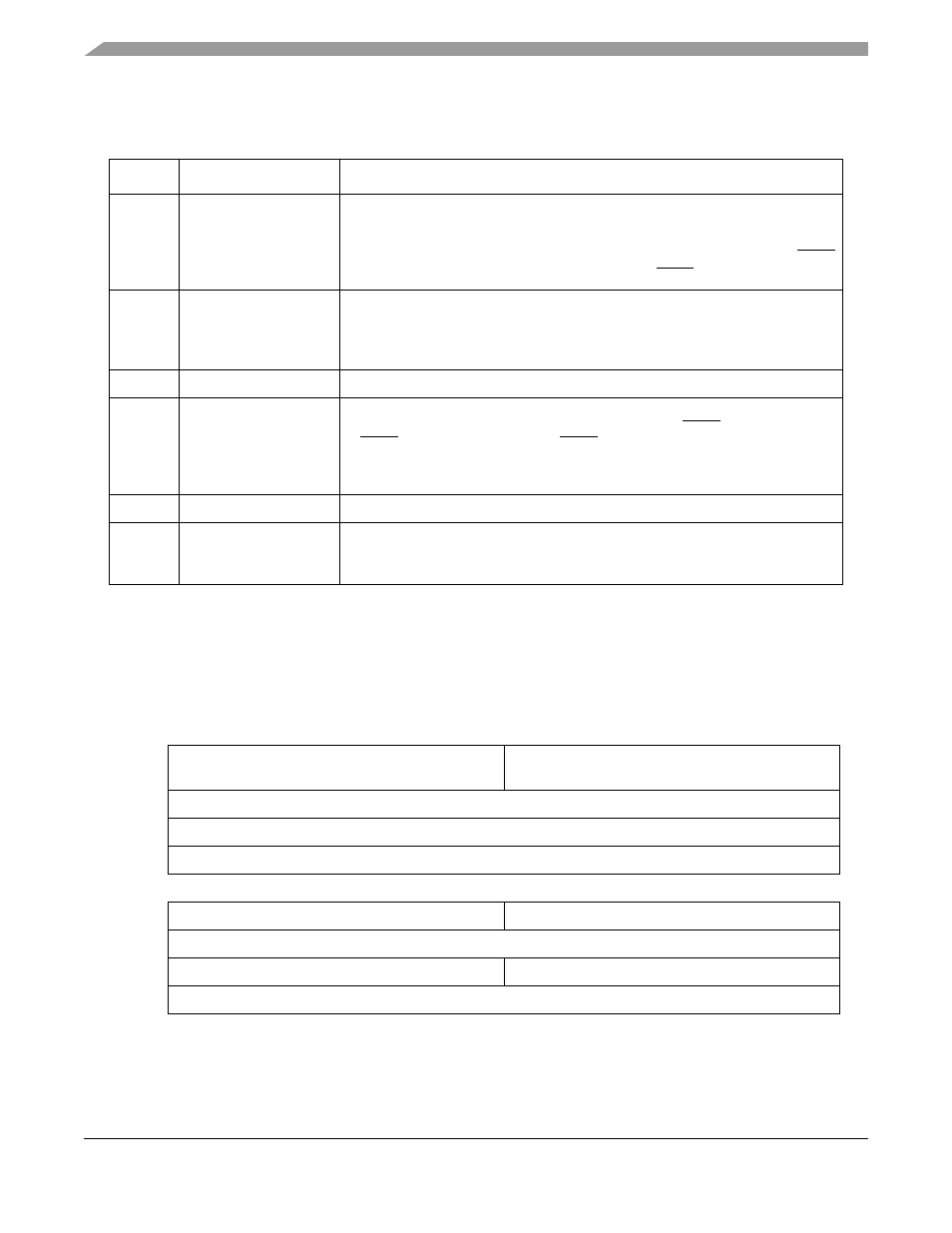

9.11.2.24 PCI Hot Swap Register Block

The PCI Hot Swap register block, shown in

, is a set of registers in a capability structure. It

contains the Hot Swap control status register itself, as well as other fields as required by the capabilities

list format.

Figure 9-56. Hot Swap Register Block

describes the Hot Swap register block fields.

Table 9-42. PCI Bus Arbiter Configuration Register Field Description

Bit

Name

Description

15

PCI_ARB_DIS

(PCI_CFG[1] pin value)

Determines if the PCI bridge is the PCI arbiter on the PCI bus. Set or cleared by

the PIC_CFG[1] pin value after hard reset.

0 PCI bridge is the PCI arbiter.

1 PCI bridge is not the PCI arbiter. The PCI bridge presents its request on REQ0

to the external arbiter and receives its grant on GNT0.

14

Parking Mode

Controls which device receives the bus grant when there are no outstanding bus

requests and the bus is idle.

0 The bus is parked with the last device to use the bus.

1 The bus is parked with the PCI bridge.

13–7

—

Reserved, should be cleared.

6-4

PCI Bus Master

Priorities

Determines the arbitration priority given to the different masters on the PCI bus.

Bit 6 corresponds to the priority of the master sourcing REQ0, bit 5 corresponds

to REQ1, and bit 4 corresponds to REQ2.

0 Master

n

has a low priority.

1 Master

n

has a high priority.

3–1

—

Reserved, should be cleared.

0

PCI Bridge Master

Priority

Determines the PCI bridge’s arbitration priority.

0 The PCI bridge has a low priority.

1 The PCI bridge has a high priority.

31

24

23

16

Field

—

HS_CSR (See

Section 9.11.2.25, “PCI Hot Swap

.”)

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x4A

15

8

7

0

Field

NXT_PTR

CAP_ID

Reset

0000_0000_0000_0110

R/W

R/W

R

Addr

0x48