6 user-programmable machines (upms), Table 11-34. upm interfaces signals, User-programmable machines (upms) -63 – Freescale Semiconductor MPC8260 User Manual

Page 481: Upm interfaces signals -63, Section 11.5.4, “differences between, Mpc8xx’s gpcm and mpc82xx’s gpcm

Memory Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

11-63

11.5.4

Differences between MPC8xx’s GPCM and MPC82xx’s GPCM

Users familiar with the MPC8xx GPCM should read this section first:

•

External termination—In the MPC8xx the external termination connects to the external bus TA and

so must be asserted in sync with the system clock. In the PowerQUICC II, this signal is separated

from the bus and named GTA. The signal is synchronized internally and sampled. The sampled

signal is used to generate TA, which terminates the bus transaction.

•

Extended hold time for reads can be up to 8 clock cycles (instead of 1 in the MPC8xx).

11.6

User-Programmable Machines (UPMs)

Users familiar with MPC8xx memory controller should first read

Section 11.6.6, “Differences between

lists the UPM interface signals on the 60x and local bus.

Additional control is available in 60x-compatible mode (60x bus only) using the external address latch

enable (ALE). However, ALE is not a UPM-controlled signal; it toggles with chip select signals.

Note that in this section, when a signal is named, the reference is to the 60x or local bus signal, according

to the bank being accessed.

The three user-programmable machines (UPMs) are flexible interfaces that connect to a wide range of

memory devices. At the heart of each UPM is an internal-memory RAM array that specifies the logical

OR0

AM1111_1110_0000_0000_0 (32 MByte)

BCTLD0

CSNT1

ACS11

SCY1111

SETA0

TRLX1

EHTR0

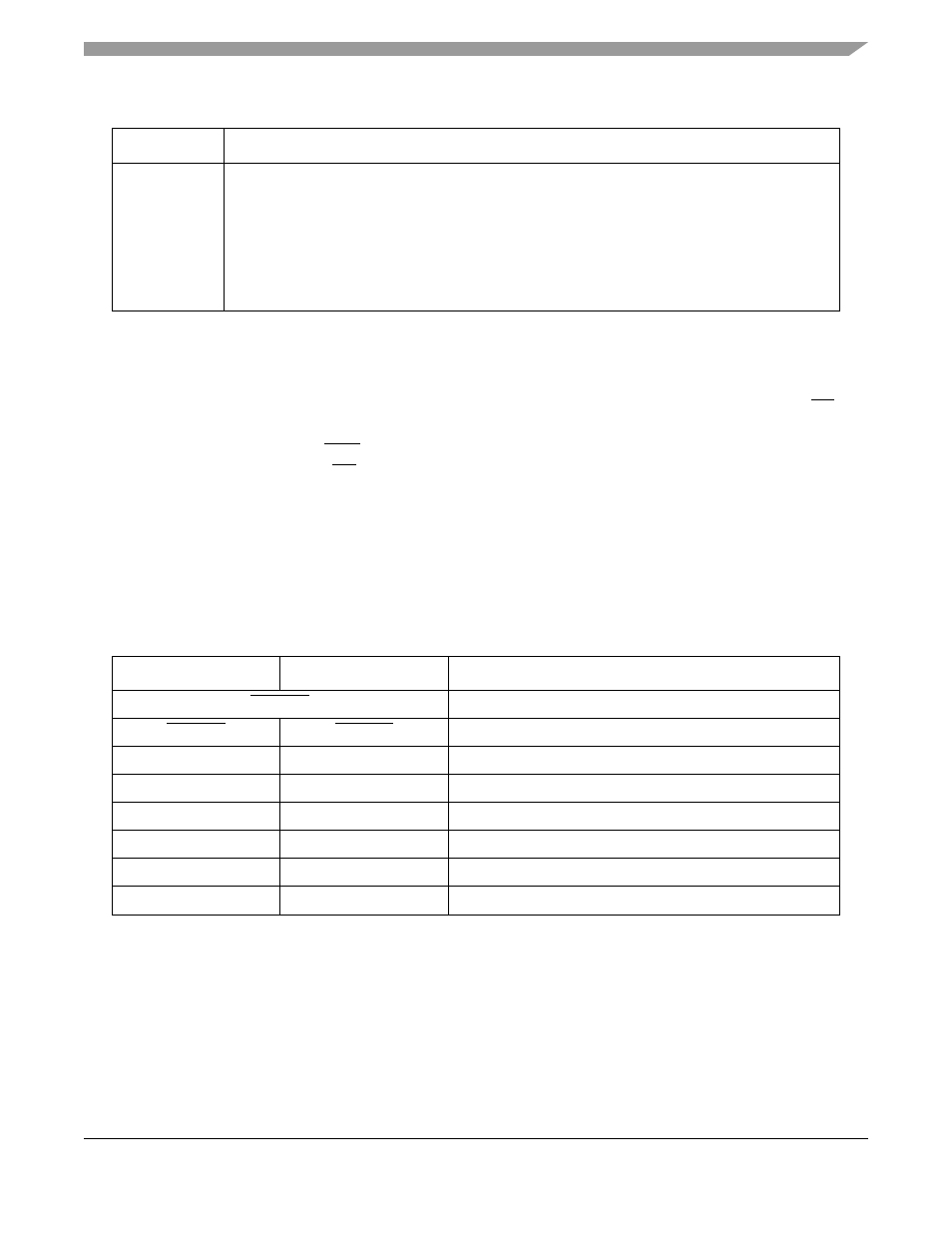

Table 11-34. UPM Interfaces Signals

60x Bus

Local Bus

Comments

CS[0–11]

Device select

PBS[0–7]

LBS[0–3]

Byte Select

PGPL_0

LGPL_0

General-purpose line 0

PGPL_1

LGPL_1

General-purpose line 1

PGPL_2

LGPL_2

General-purpose line 2

PGPL_3

LGPL_3

General-purpose line 3

PGPL_4/UPMWAIT

LGPL_4/UPMWAIT

General-purpose line 4/UPM wait

PGPL_5

LGPL_5

General-purpose line 5

Table 11-33. . Boot Bank Field Values after Reset (continued)

Register

Setting