Freescale Semiconductor MPC8260 User Manual

Page 618

CPM Multiplexing

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

16-8

Freescale Semiconductor

NOTE

Each SADx and MADx corresponds to a pair of separate receive and

transmit address pins.

The PowerQUICC II has 16 output address pins and 10 input address pins dedicated for the UTOPIA

interface. However, it has two FCCs with two parts each—receiver and transmitter that can be ether master

or slave concurrently. The PowerQUICC II allows both FCC1 and FCC2 to connect to the address lines

without putting limitations on being a master or slave, as described in the following:

•

For master mode: The user has two groups of eight address pins each. Three pins from each group

are always connected to FCC1 and three are always connected to FCC2. The user decides which

FCC uses the remaining two pins by programming CMXUAR[MADx]. See

8–9

F1IRB

FCC1 internal rate BRG selection. Selects the BRG to be connected to FCC 1 for internal rate

operation. Used by the ATM controller; see

Section 30.2.1.5, “Transmit External Rate and Internal

00 FCC1 internal rate clock is BRG5.

01 FCC1 internal rate clock is BRG6.

10 FCC1 internal rate clock is BRG7.

11 FCC1 internal rate clock is BRG8.

10–11

F12IRB FCC2 internal rate BRG selection. Selects the BRG to be connected to FCC 2 for internal rate

operation. Used by the ATM controller; see

Section 30.2.1.5, “Transmit External Rate and Internal

00 FCC2 internal rate clock is BRG5.

01 FCC2 internal rate clock is BRG6.

10 FCC2 internal rate clock is BRG7.

11 FCC2 internal rate clock is BRG8.

12–15

—

Reserved, should be cleared.

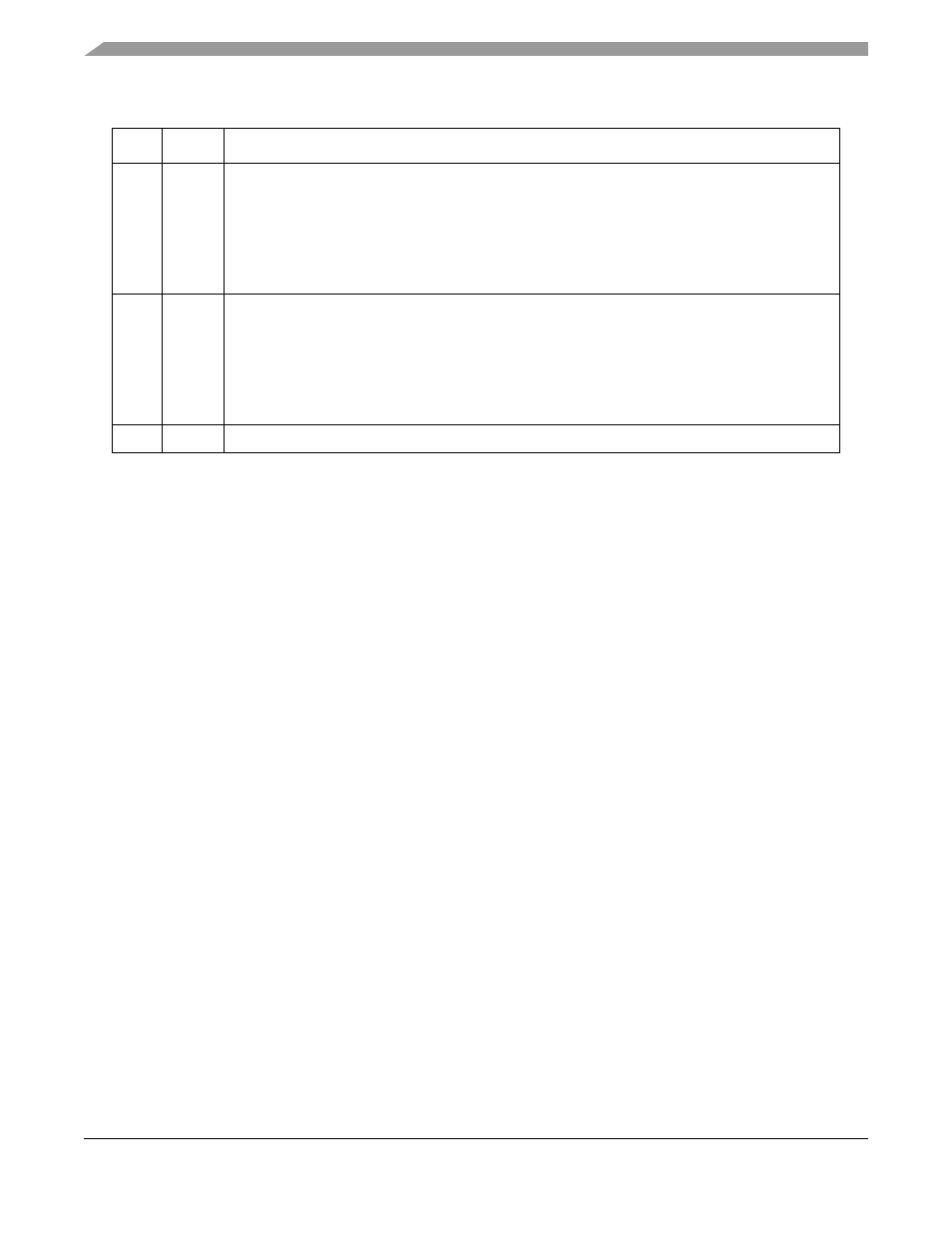

Table 16-2. CMXUAR Field Descriptions (continued)

Bits

Name

Description