Freescale Semiconductor MPC8260 User Manual

Page 161

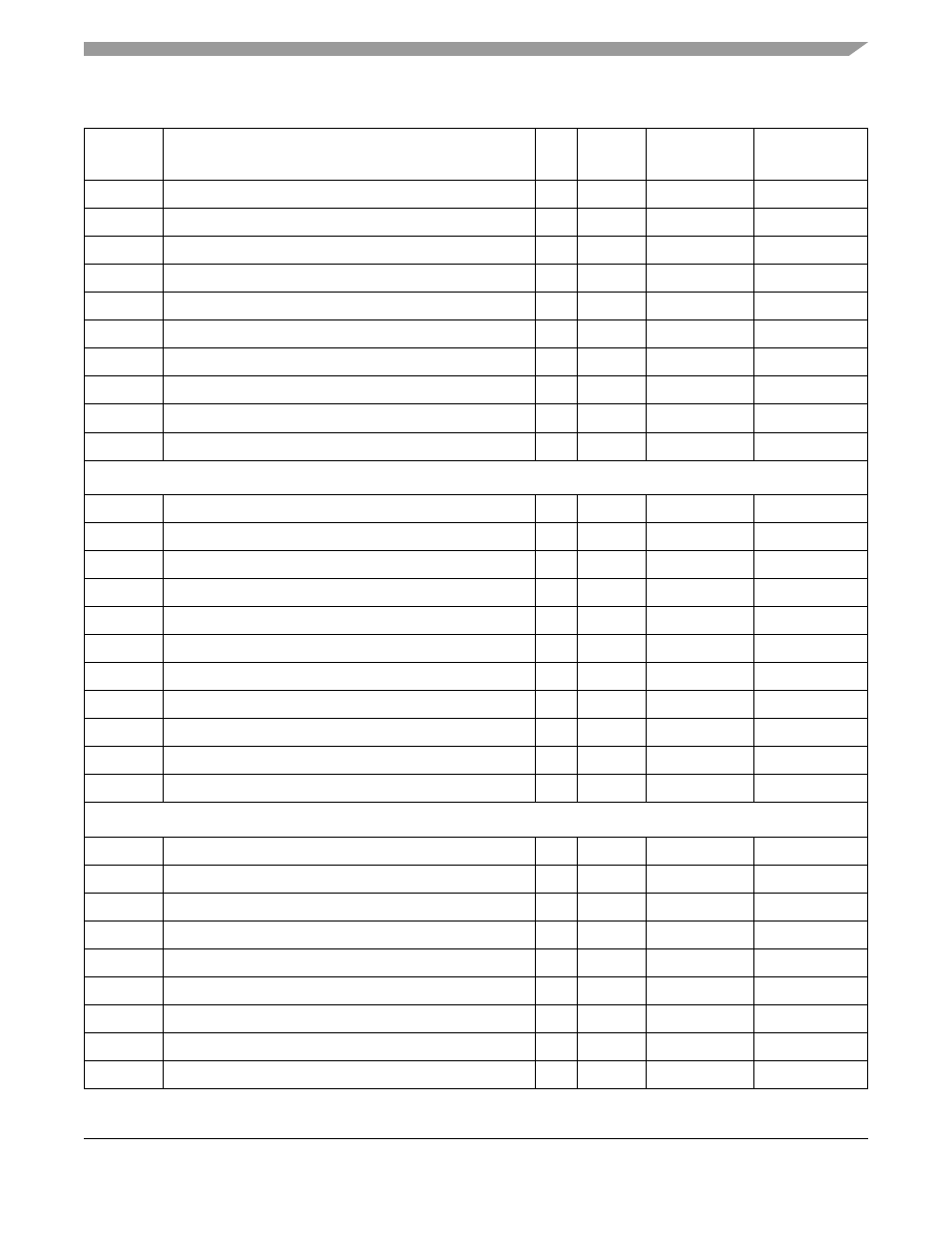

Memory Map

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

3-15

0x114A2

TC6 cell delineation state machine register (CDSMR6)

4

R/W

16 bits

0x0000

0x114A4

TC6 event register (TCER6)

4

R/W

16 bits

0x0000

0x114A6

TC6 received cells counter (TC_RCC6)

4

R/W

16 bits

0x0000

0x114A8

TC6 mask register (TCMR6)

4

R/W

16 bits

0x0000

0x114AA

TC6 filtered cells counter (TC_FCC6)

4

R/W

16 bits

0x0000

0x114AC

TC6 corrected cells counter (TC_CCC6)

4

R/W

16 bits

0x0000

0x114AE

TC6 idle cells counter (TC_ICC6)

4

R/W

16 bits

0x0000

0x114B0

TC6 transmitted cells counter (TC_TCC6)

4

R/W

16 bits

0x0000

0x114B2

TC6 error cells counter (TC_ECC6)

4

R/W

16 bits

0x0000

0x114B4

Reserved

—

12 bytes

—

—

TC Layer 7

4

0x114C0

TC7 mode register (TCMODE7)

4

R/W

16 bits

0x0000

0x114C2

TC7 cell delineation state machine register (CDSMR7)

4

R/W

16 bits

0x0000

0x114C4

TC7 event register (TCER7)

4

R/W

16 bits

0x0000

0x114C6

TC7 received cells counter (TC_RCC7)

4

R/W

16 bits

0x0000

0x114C8

TC7 mask register (TCMR7)

4

R/W

16 bits

0x0000

0x114CA

TC7 filtered cells counter (TC_FCC7)

4

R/W

16 bits

0x0000

0x114CC

TC7 corrected cells counter (TC_CCC7)

4

R/W

16 bits

0x0000

0x114CE

TC7 idle cells counter (TC_ICC7)

4

R/W

16 bits

0x0000

0x114D0

TC7 transmitted cells counter (TC_TCC7)

4

R/W

16 bits

0x0000

0x114D2

TC7 error cells counter (TC_ECC7)

4

R/W

16 bits

0x0000

0x114D4

Reserved

—

12 bytes

—

—

TC Layer 8

4

0x114E0

TC8 mode register (TCMODE8)

4

R/W

16 bits

0x0000

0x114E2

TC8 cell delineation state machine register (CDSMR8)

4

R/W

16 bits

0x0000

0x114E4

TC8 event register (TCER8)

4

R/W

16 bits

0x0000

0x114E6

TC8 received cells counter (TC_RCC8)

4

R/W

16 bits

0x0000

0x114E8

TC8 mask register (TCMR8)

4

R/W

16 bits

0x0000

0x114EA

TC8 filtered cells counter (TC_FCC8)

4

R/W

16 bits

0x0000

0x114EC

TC8 corrected cells counter (TC_CCC8)

4

R/W

16 bits

0x0000

0x114EE

TC8 idle cells counter (TC_ICC8)

4

R/W

16 bits

0x0000

0x114F0

TC8 transmitted cells counter (TC_TCC8)

4

R/W

16 bits

0x0000

Table 3-1. Internal Memory Map (continued)

Address

(offset)

Register

R/W

Size

Reset

Section/Page