Figure 4-9. interrupt request masking, 4 interrupt vector generation and calculation, Interrupt vector generation and calculation -14 – Freescale Semiconductor MPC8260 User Manual

Page 186: Interrupt request masking -14, Encoding the interrupt vector -14, Figure 4-9

System Interface Unit (SIU)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

4-14

Freescale Semiconductor

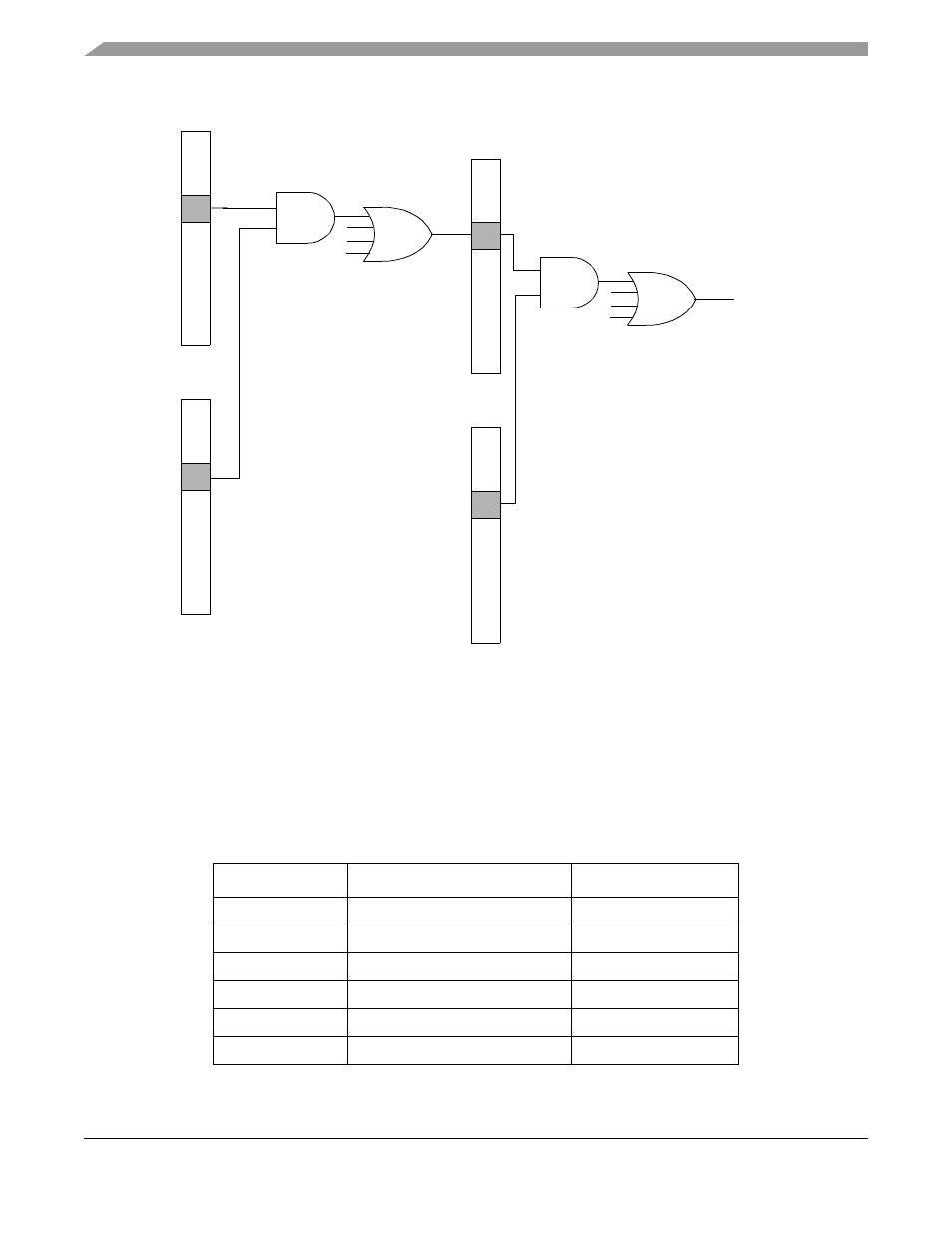

Figure 4-9. Interrupt Request Masking

4.2.4

Interrupt Vector Generation and Calculation

Pending unmasked interrupts are presented to the core in order of priority. The interrupt vector that allows

the core to locate the interrupt service routine is made available to the core by reading SIVEC. The

interrupt controller passes an interrupt vector corresponding to the highest-priority, unmasked, pending

interrupt.

lists encodings for the six low-order bits of the interrupt vector.

Table 4-3. Encoding the Interrupt Vector

Interrupt Number

Interrupt Source Description

Interrupt Vector

0

Error (No interrupt)

0b00_0000

1

I

2

C

0b00_0001

2

SPI

0b00_0010

3

RISC Timers

0b00_0011

4

SMC1

0b00_0100

5

SMC2

0b00_0101

SCCE

SCCM

13 Input (or

SIPNR

Mask

Bit

SIMR

(Other Unmasked Requests)

Request to

the core

Mask

Bit

Event

Bit

13 Event Bits)