Freescale Semiconductor MPC8260 User Manual

Page 169

Memory Map

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

3-23

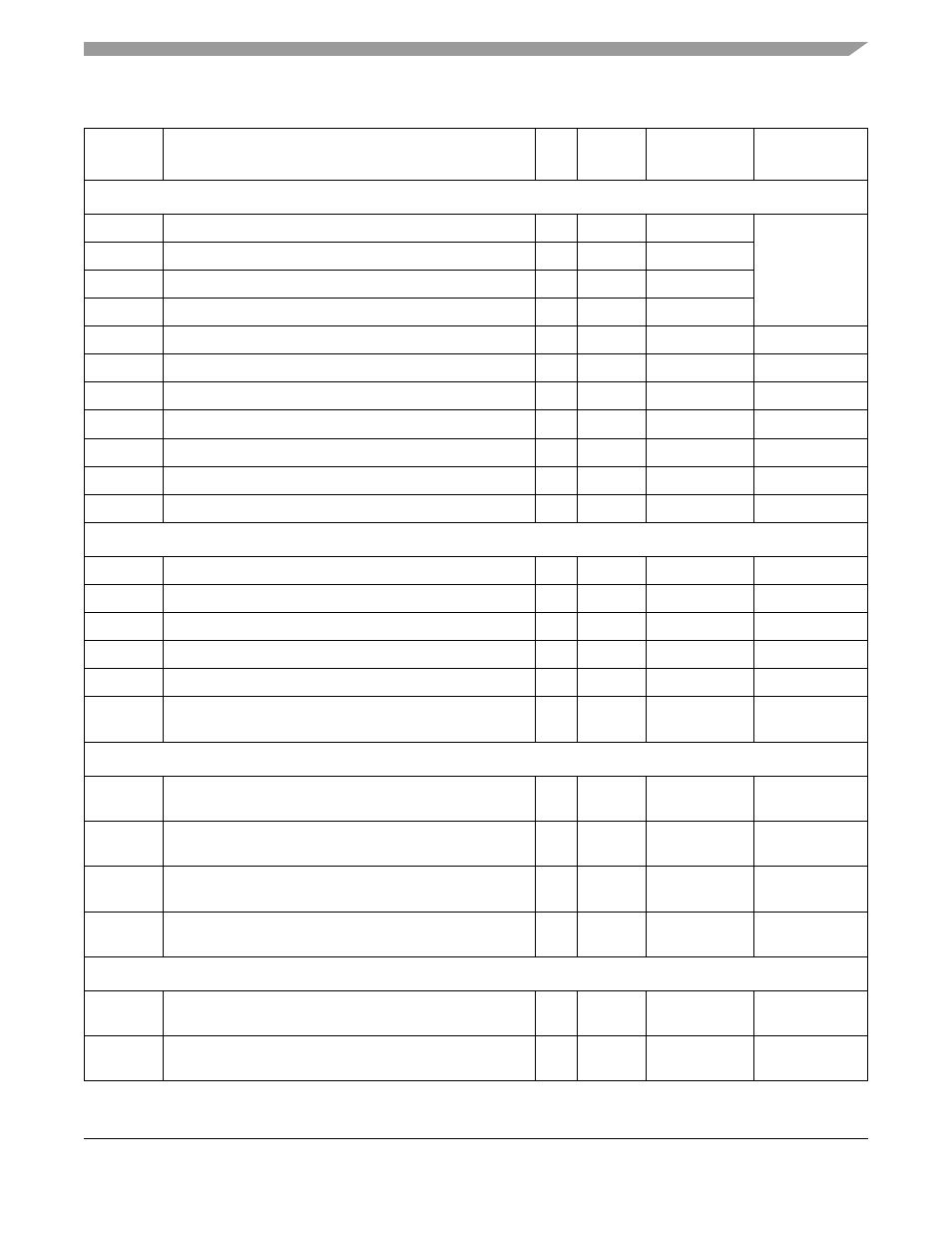

SI2 Registers

0x11B40

SI2 TDMA2 mode register (SI2AMR)

R/W

16 bits

0x0000

0x11B42

SI2 TDMB2 mode register (SI2BMR)

R/W

16 bits

0x0000

0x11B44

SI2 TDMC2 mode register (SI2CMR)

R/W

16 bits

0x0000

0x11B46

SI2 TDMD2 mode register (SI2DMR)

R/W

8 bits

0x0000

0x11B48

SI2 global mode register (SI2GMR)

R/W

8 bits

0x00

0x11B49

Reserved

—

8 bits

—

—

0x11B4A

SI2 command register (SI2CMDR)

R/W

8 bits

0x00

0x11B4B

Reserved

—

8 bits

—

—

0x11B4C

SI2 status register (SI2STR)

R/W

8 bits

0x00

0x11B4D

Reserved

—

16 bits

—

—

0x11B4E

SI2 RAM shadow address register (SI2RSR)

R/W

16 bits

0x0000

MCC2 Registers

0x11B50

MCC2 event register (MCCE2)

R/W

16 bits

0x0000

0x11B52

Reserved

—

16 bits

—

—

0x11B54

MCC2 mask register (MCCM2)

R/W

16 bits

0x0000

0x11B56

Reserved

—

16 bits

—

—

0x11B58

MCC2 configuration register (MCCF2)

R/W

8 bits

0x00

0x11B59–

0x11FFF

Reserved

—

1,159

bytes

—

—

SI1 RAM

0x12000–

0x121FF

SI 1 transmit routing RAM (SI1TxRAM)

R/W

512

bytes

undefined

0x12200–

0x123FF

Reserved

—

512

bytes

—

—

0x12400–

0x125FF

SI 1 receive routing RAM (SI1RxRAM)

R/W

512

bytes

undefined

0x12600–

0x127FF

Reserved

—

512

bytes

—

—

SI2 RAM

0x12800–

0x129FF

SI 2 transmit routing RAM (SI2TxRAM)

R/W

512

bytes

undefined

0x12A00–

0x12BFF

Reserved

—

512

bytes

—

—

Table 3-1. Internal Memory Map (continued)

Address

(offset)

Register

R/W

Size

Reset

Section/Page