Freescale Semiconductor MPC8260 User Manual

Page 167

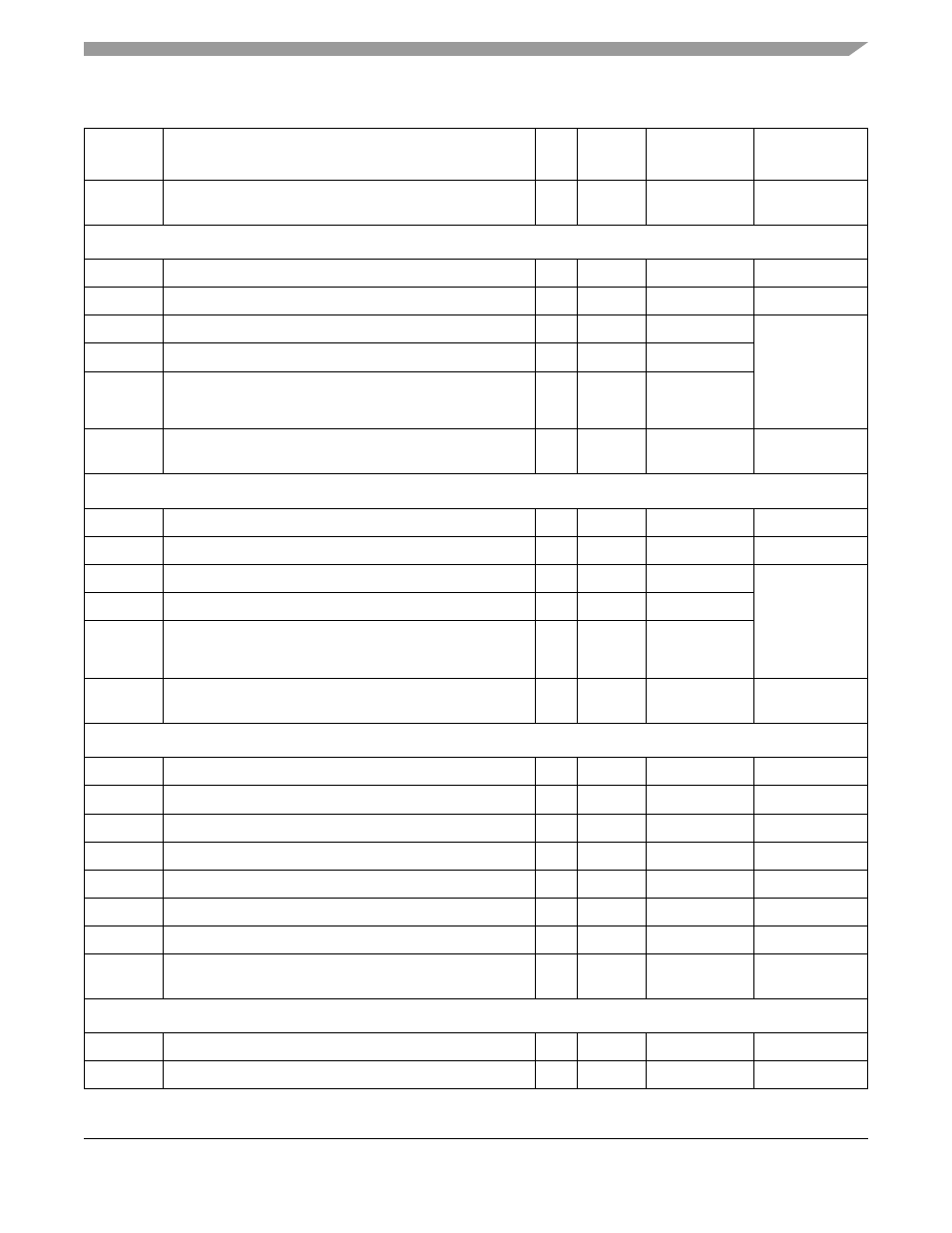

Memory Map

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

3-21

0x11A78–

0x11A7F

Reserved

—

8 bytes

—

—

SMC1

0x11A82 SMC1 mode register (SMCMR1)

R/W

16 bits

0x0000

0x11A84 Reserved

—

16

bits

—

—

0x11A86

SMC1 event register (SMCE1)

R/W

8 bits

0x00

(UART)

(Transparent)

(GCI)

0x11A87

Reserved

—

24 bits

—

0x11A8A

SMC1 mask register (SMCM1)

R/W

8 bits

0x00

0x11A8B–

0x11A91

Reserved

—

7 bytes

—

—

SMC2

0x11A92 SMC2 mode register (SMCMR2)

R/W

16 bits

0x0000

0x11A94 Reserved

—

16

bits

—

—

0x11A96

SMC2 event register (SMCE2)

R/W

8 bits

0x00

(UART)

(Transparent)

(GCI)

0x11A97

Reserved

—

24 bits

—

0x11A9A

SMC2 mask register (SMCM2)

R/W

8 bits

0x00

0x11A9B–

0x11A9F

Reserved

—

5 bytes

—

—

SPI

0x11AA0 SPI mode register (SPMODE)

R/W

16 bits

0x0000

0x11AA2

Reserved

—

4 bytes

—

—

0x11AA6 SPI event register (SPIE)

R/W

8 bits

0x00

0x11AA7

Reserved

—

24 bits

—

—

0x11AAA SPI mask register (SPIM)

R/W

8 bits

0x00

0x11AAB

Reserved

—

24 bits

—

—

0x11AAD SPI command register (SPCOM)

W

8 bits

0x00

0x11AAE–

0x11AFF

Reserved

—

82 bytes

—

—

CPM Mux

0x11B00

CPM mux SI1 clock route register (CMXSI1CR)

R/W

8 bits

0x00

0x11B02

CPM mux SI2 clock route register (CMXSI2CR)

R/W

8 bits

0x00

Table 3-1. Internal Memory Map (continued)

Address

(offset)

Register

R/W

Size

Reset

Section/Page