Figure 11-41. gpcm peripheral device interface, 2 chip-select and write enable deassertion timing, Gpcm peripheral device interface -54 – Freescale Semiconductor MPC8260 User Manual

Page 472

Memory Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

11-54

Freescale Semiconductor

•

One quarter of a clock cycle later

•

One half of a clock cycle later

Note the GPCM does not negate CS in back-to-back reads to the same device when in single

PowerQUICC II bus mode or in 60x-compatible bus mode with extended transfers enabled. When in strict

60x bus mode, however, the GPCM does negate CS in back-to-back reads. See

Configuration Register (BCR).”

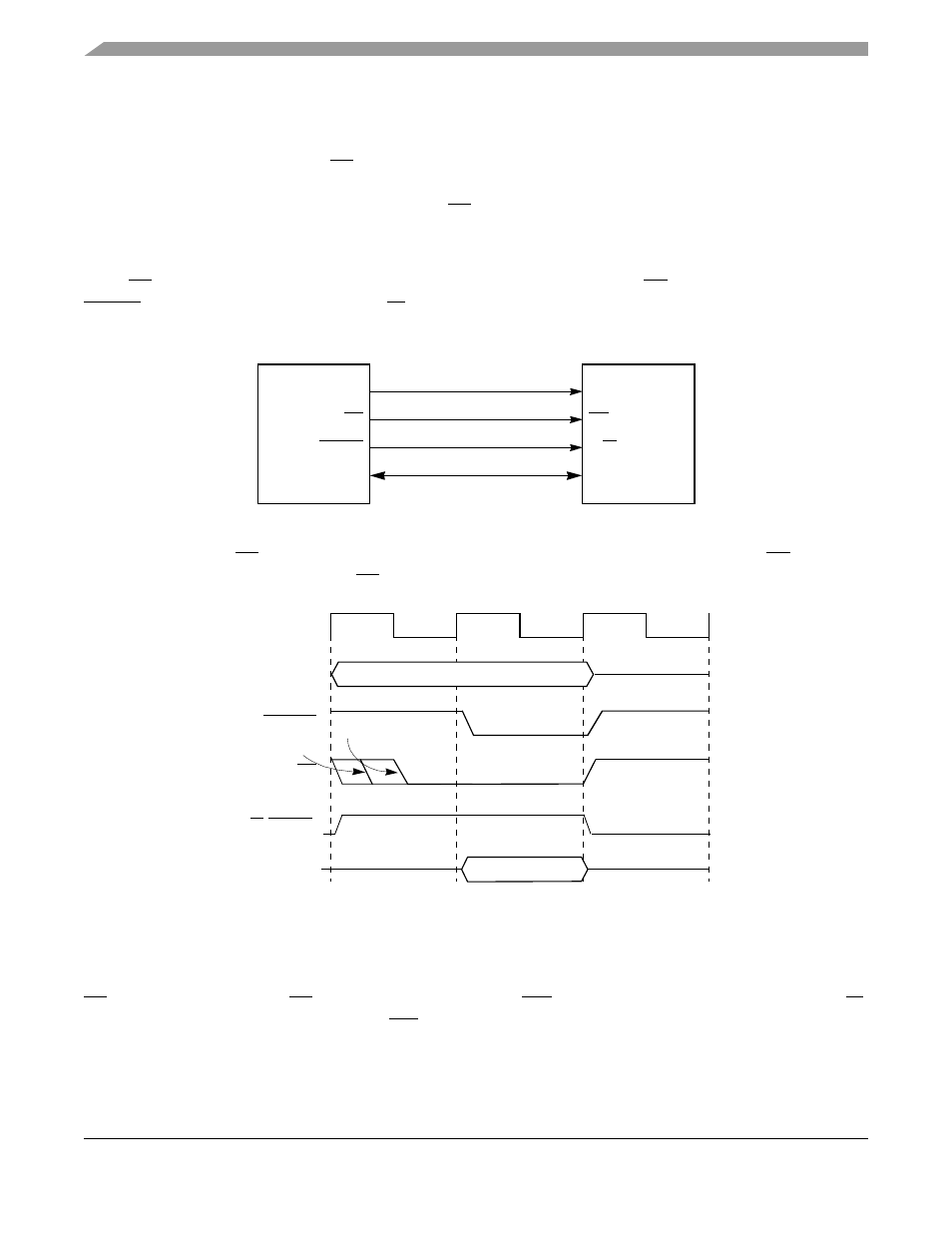

shows a basic connection between the PowerQUICC II and an external peripheral device.

Here, CS (the strobe output for the memory access) is connected directly to CE of the memory device and

BCTL0 is connected to the respective R/W in the peripheral device.

Figure 11-41. GPCM Peripheral Device Interface

shows CS as defined by the setup time required between the address lines and CE. The user

can configure ORx[ACS] to specify CS to meet this requirement.

Figure 11-42. GPCM Peripheral Device Basic Timing (ACS = 1x and TRLX = 0)

11.5.1.2

Chip-Select and Write Enable Deassertion Timing

shows a basic connection between the PowerQUICC II and a static memory device. Here,

CS is connected directly to CE of the memory device. The WE signals are connected to the respective W

signal in the memory device where each WE corresponds to a different data byte.

Address

CE

R/W

Data

Peripheral

Data

BCTL0

CS

Address

PowerQUI

Clock

Address

PSDVAL

CS

R/W(BCTL0)

Data

ACS = 11

ACS = 10