Figure 4-26. lcl_alrh, Lcl_alrh -32 – Freescale Semiconductor MPC8260 User Manual

Page 204

System Interface Unit (SIU)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

4-32

Freescale Semiconductor

4.3.2.5

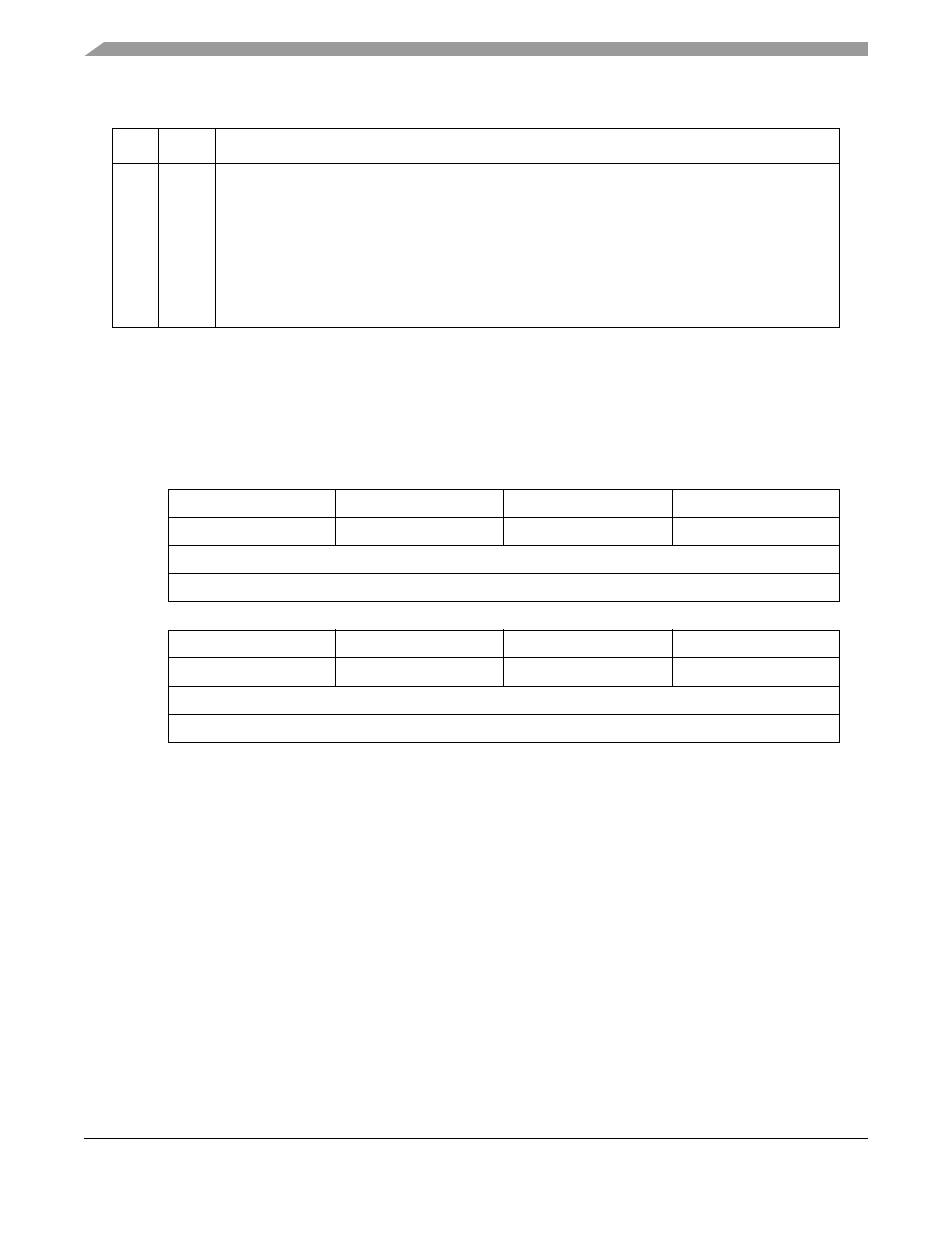

Local Bus Arbitration Level Registers (LCL_ALRH and LCL_ACRL)

The local bus arbitration level registers (LCL_ALRH and LCL_ALRL), shown in

, define arbitration priority for local bus masters 0–7. Priority field 0 has highest-priority. For

information about the PowerQUICC II local bus master indexes see LCL_ACR[PRKM] in

LCL_ALRL, shown in

, defines arbitration priority of PowerQUICC II local bus masters 8–15.

4–7

PRKM

Parking master. Defines the parked master.

0000 CPM high request level refers to the IDMA which involves peripherals and the following serial

channels (SCC, SPI, SMC, and I

2

C)

0001 CPM middle request level refers to all other serial channels (FCCs and MCCs)

0010 CPM low request level: it is possible to change the request level for all FCCs and MCCs to low

priority when PPC_ACR[4–7] = 0010 and FCRx[1] = 1 (See Section 28.7.1, “FCC Function

Code Registers (FCRx).”

0011 Host bridge

Values 0100–1111 are reserved.

0

3

4

7

8

11

12

15

Field

Priority Field 0

Priority Field 1

Priority Field 2

Priority Field 3

Reset

0000

0001

0010

0110

R/W

R/W

Addr

16

19

20

23

24

27

28

31

Field

Priority Field 4

Priority Field 5

Priority Field 6

Priority Field 7

Reset

0011

0100

0101

0111

R/W

R/W

Addr

0x10040

Figure 4-26. LCL_ALRH

Table 4-11. LCL_ACR Field Descriptions (continued)

Bits

Name

Description