Table 9-71. dmabcrx field descriptions, Table 9-72. dmandarx field descriptions, Dmabcrx field descriptions -94 – Freescale Semiconductor MPC8260 User Manual

Page 400: Dmandarx field descriptions -94, Section 9.13.1.6.7, “dma next descriptor address, Register [0–3] (dmandarx), Table 9-72 describes dmandar x fields

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

9-94

Freescale Semiconductor

9.13.1.6.7

DMA Next Descriptor Address Register [0–3] (DMANDAR

x

)

The next descriptor address register (NDAR) contains the address for the next segment descriptor in the

chain. In chaining mode, this register is loaded from the “next descriptor” field of the descriptor that the

current descriptor register is pointing to. Refer to

.

Figure 9-88. DMA Next Descriptor Address Register [0–3] (DMANDAR

x)

describes DMANDARx fields.

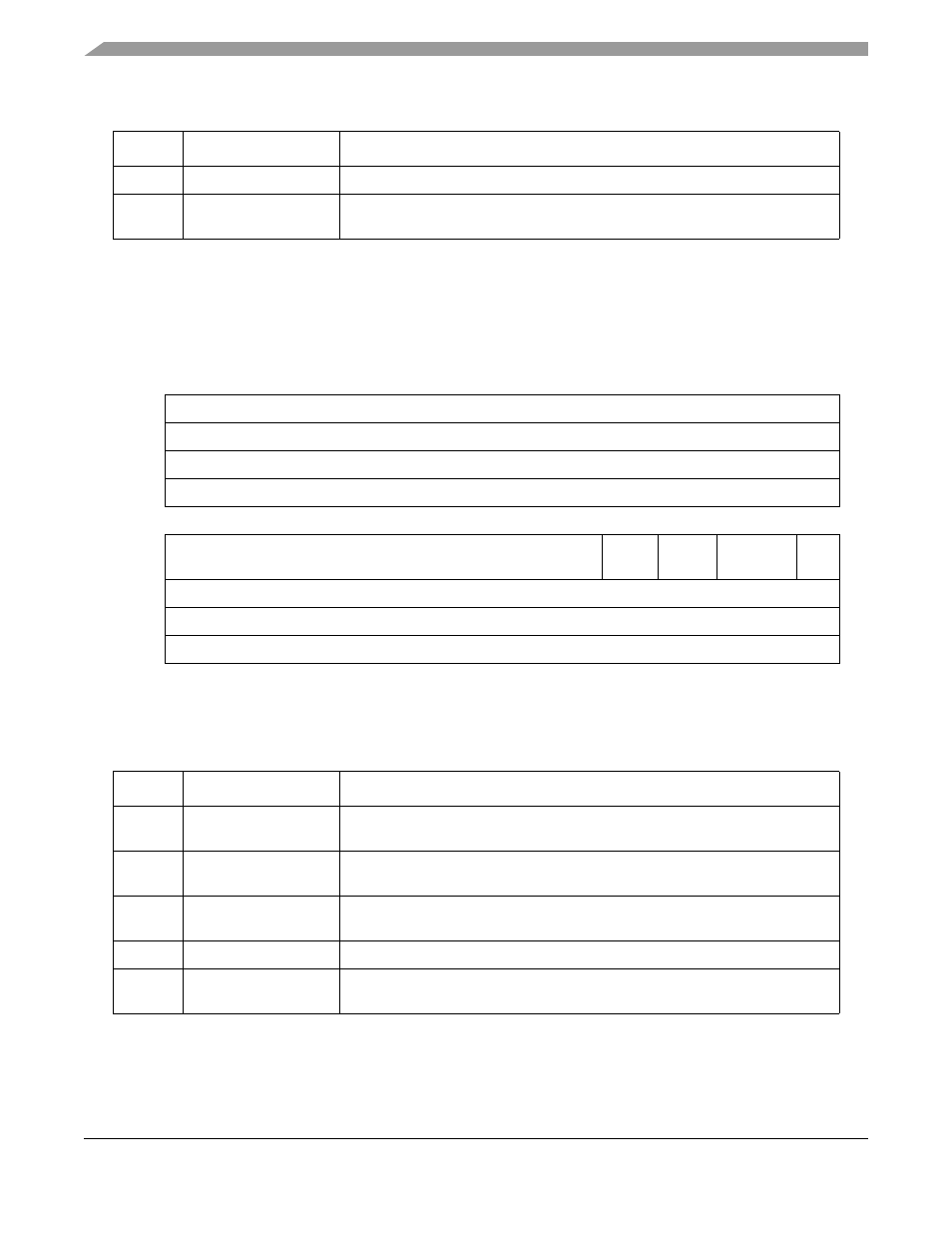

Table 9-71. DMABCR

x Field Descriptions

Bit

Name

Description

31–26

—

Reserved, should be cleared.

25–0

BC

Byte count. Contains the number of bytes to transfer. The value in this register is

decremented after each DMA read operation.

31

16

Field

NDA

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10526 (DMANDAR0); 0x105A6 (DMANDAR1); 0x10626 (DMANDAR2); 0x106A6 (DMANDAR3)

15

5

4

3

2

1

0

Field

NDA

NDSNE

N

NDEOSIE

—

EOTD

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10524 (DMANDAR0); 0x105A4 (DMANDAR1); 0x10624 (DMANDAR2); 0x106A4 (DMANDAR3)

Table 9-72. DMANDAR

x Field Descriptions

Bit

Name

Description

31–5

NDA

Next descriptor address. Contains the next descriptor address of the segment

descriptor in memory. It must be aligned on an 8-word (32-byte) boundary.

4

NDSNEN

Next descriptor snoop enable. When set will allow snooping on DMA

transactions.

3

NDEOSIE

Next descriptor end-of-segment interrupt enable. When set will generate an

interrupt at the end of this DMA transfer.

2–1

—

Reserved, should be cleared.

0

EOTD

End-of-transfer descriptor. When set indicates that this descriptor is the last one

to be executed.