17 scc uart receive buffer descriptor (rxbd), Scc uart receive buffer descriptor (rxbd) -14 – Freescale Semiconductor MPC8260 User Manual

Page 718

SCC UART Mode

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

21-14

Freescale Semiconductor

21.17 SCC UART Receive Buffer Descriptor (RxBD)

The CPM uses RxBDs to report on each buffer received. The CPM closes the current buffer, generates a

maskable interrupt, and starts receiving data into the next buffer after one of the following occurs:

•

A user-defined control character is received.

•

An error occurs during message processing.

•

A full receive buffer is detected.

•

A MAX_IDL number of consecutive idle characters is received.

7

RZS

Receive zero stop bits.

0 The receiver operates normally, but at least one stop bit is needed between characters. A framing

error is issued if a stop bit is missing. Break status is set if an all-zero character is received with

a zero stop bit.

1 Configures the receiver to receive data without stop bits. Useful in V.14 applications where SCC

UART controller data is supplied synchronously and all stop bits of a particular character can be

omitted for cross-network rate adaptation. RZS should be set only if SYN is set. The receiver

continues if a stop bit is missing. If the stop bit is a zero, the next bit is considered the first data

bit of the next character. A framing error is issued if a stop bit is missing, but a break status is

reported only after two consecutive break characters have no stop bits.

8

SYN

Synchronous mode.

0 Normal asynchronous operation. GSMR_L[TENC,RENC] must select NRZ and GSMR_L[TDCR,

RDCR] select either 8

Ч, 16Ч, or 32Ч. 16Ч is recommended for most applications.

1 Synchronous SCC UART controller using 1

× clock (isochronous UART operation).

GSMR_L[TENC, RENC] must select NRZ and GSMR_L[RDCR, TDCR] select 1

× mode. A bit is

transferred with each clock and is synchronous to the clock, which can be internal or external.

9

DRT

Disable receiver while transmitting.

0 Normal operation.

1 While the SCC is sending data, the internal RTS disables and gates the receiver. Useful for a

multidrop configuration in which the user does not want to receive its own transmission. For

multidrop UART mode, set the BDs’ preamble bit, TxBD[P].

Note: If DRT = 1, GSMR_H[CDS] should be cleared unless both of the following are true: the same

clock is used for TCLK and RCLK, and CTS either has synchronous timing or is always

asserted.

10

—

Reserved, should be cleared.

11

PEN

Parity enable.

0 No parity.

1 Parity is enabled and determined by the parity mode bits.

12–13,

14–15

RPM,

TPM

Receiver/transmitter parity mode. Selects the type of parity check the receiver/transmitter performs;

can be modified on-the-fly. Receive parity errors can be ignored but not disabled.

00 Odd parity. If a transmitter counts an even number of ones in the data word, it sets the parity bit

so an odd number is sent. If a receiver receives an even number, a parity error is reported.

01 Low parity (space parity). A transmitter sends a zero in the parity bit position. If a receiver does

not read a 0 in the parity bit, a parity error is reported.

10 Even parity. Like odd parity, the transmitter adjusts the parity bit, as necessary, to ensure that

the receiver receives an even number of one bits; otherwise, a parity error is reported.

11 High parity (mark parity). The transmitter sends a one in the parity bit position. If the receiver

does not read a 1 in the parity bit, a parity error is reported.

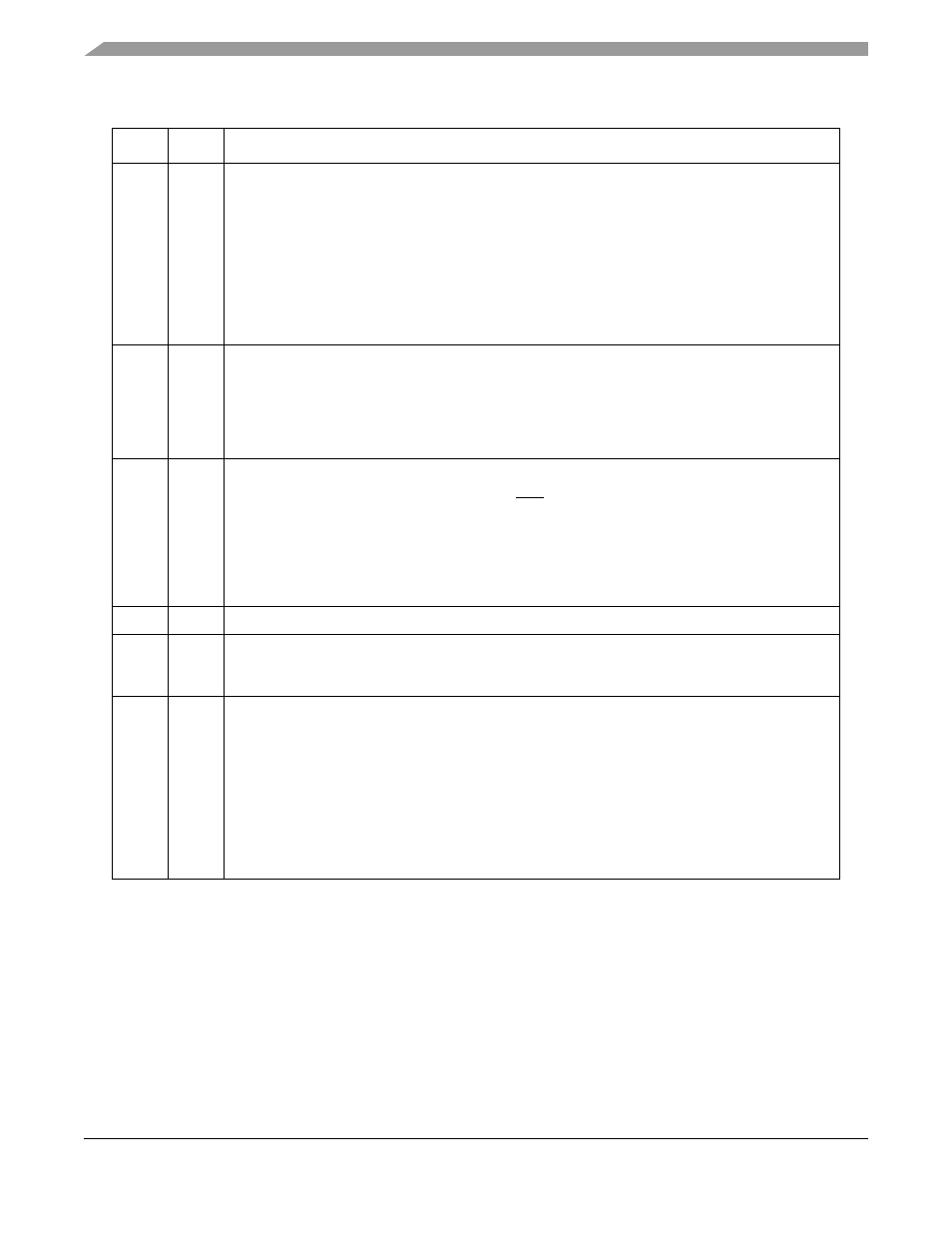

Table 21-9. PSMR UART Field Descriptions (continued)

Bit

Name

Description