Freescale Semiconductor MPC8260 User Manual

Page 522

Memory Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

11-104

Freescale Semiconductor

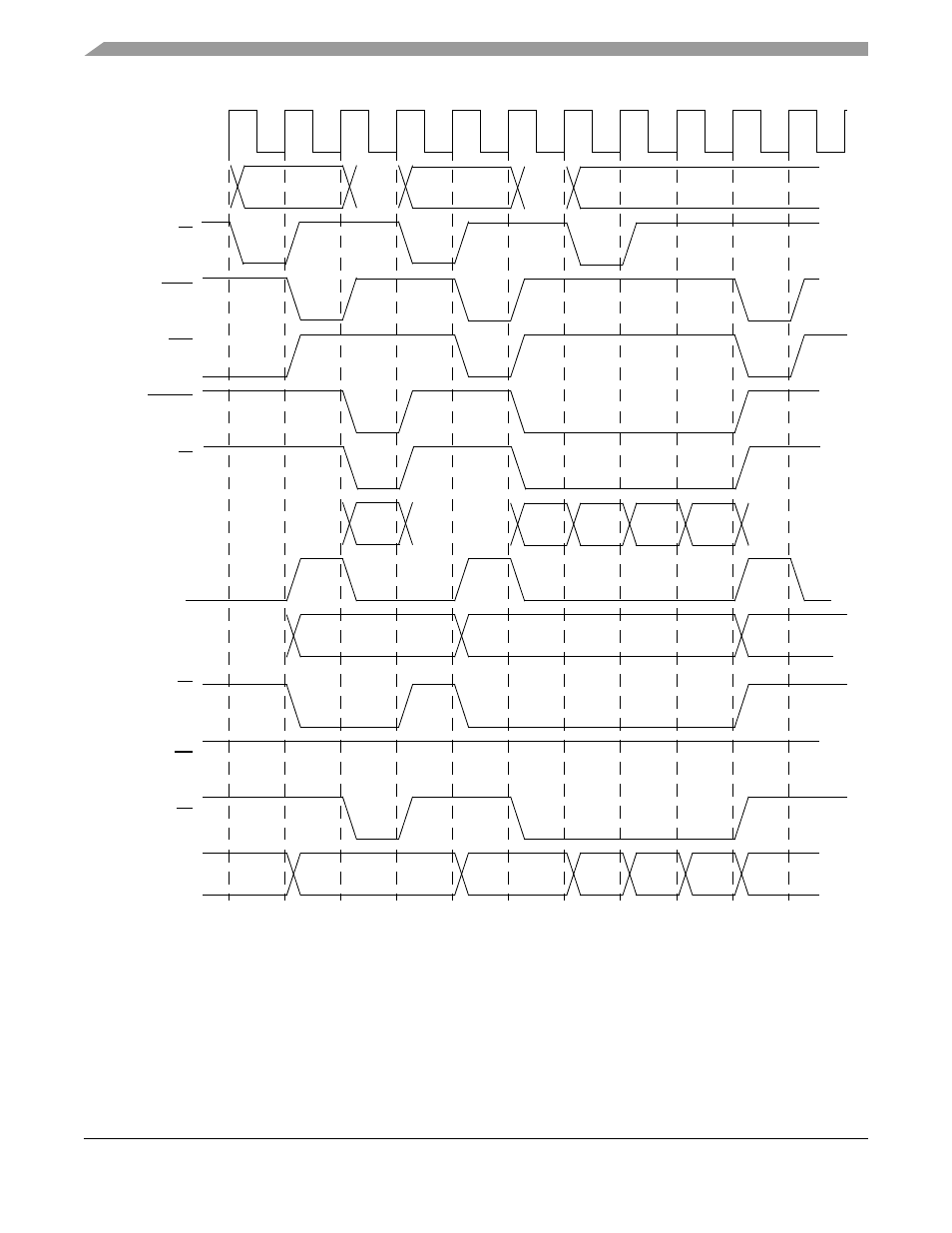

Figure 11-84. Pipelined Bus Operation and Memory Access in 60x-Compatible Mode

shows the 1-cycle delay for external master access. For systems that use the 60x bus with low

frequency (33 MHz), the 1-cycle delay for external masters can be eliminated by setting BCR[EXDD].

CLKIN

ADDR + ATTR

TS

AACK

DBG

PSDVAL

D

TA

CS

WE

OE

BADDR[27–28]

ALE

MA

00

01

02

03