7 uni statistics table, Table 30-41. uni statistics table, 11 atm exceptions – Freescale Semiconductor MPC8260 User Manual

Page 1001: 1 interrupt queues, Uni statistics table -81, Atm exceptions -81, Interrupt queues -81, Section 30.10.7, “uni statistics table

ATM Controller and AAL0, AAL1, and AAL5

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

30-81

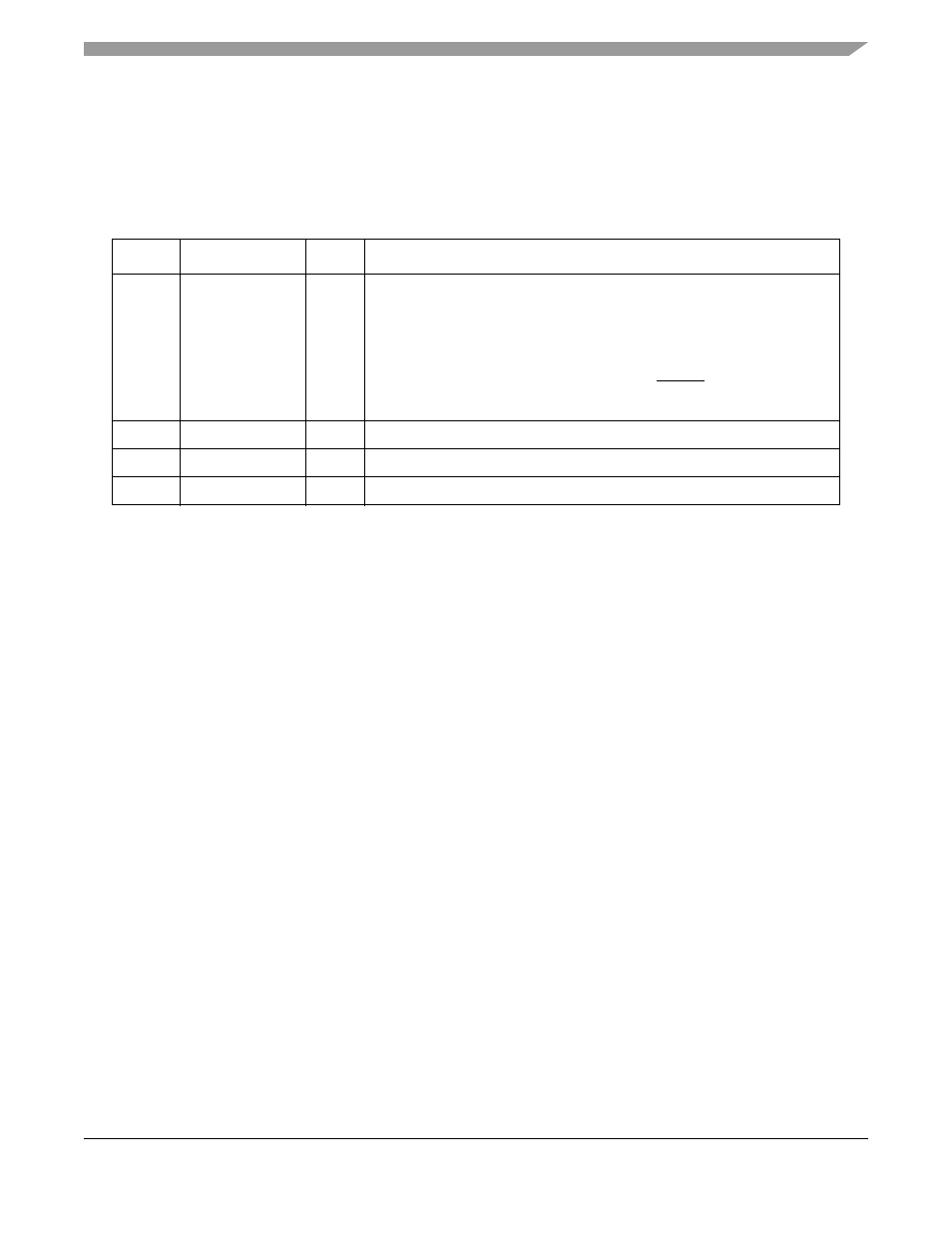

30.10.7 UNI Statistics Table

The UNI statistics table, shown in

, resides in the dual-port RAM and holds UNI statistics

parameters. UNI_STATT_BASE points to the base address of this table. Each PHY’s own table has a

starting address given by UNI_STATT_BASE+ PHY#

× 8.

30.11 ATM Exceptions

The ATM controller interrupt handling involves two principal data structures: FCCEs (FCC event

registers) and circular interrupt queues.

Four priority interrupt queues are available. By programming RCT[INTQ] and TCT[INTQ], the user

determines which queue receives the interrupt. Channel Rx buffer, Rx frame, or Tx buffer events can be

masked by clearing interrupt mask bits in RCT and TCT.

After an interrupt request, the host reads FCCE. If FCCE[GINTx] = 1, at least one entry was added to one

of the interrupt queues. After clearing FCCE[GINTx], the host processes the valid interrupt queue entries

and clears each entry’s valid bit. The host follows this procedure until it reaches an entry with V = 0. See

Section 30.11.2, “Interrupt Queue Entry.”

The host controls the number of interrupts sent to the core using a down counter in the interrupt queue’s

parameter table; see Section 30.11.3. For each event sent to an interrupt queue, a counter (that has been

initialized to a threshold number of interrupts) is decremented. When the counter reaches zero, the global

interrupt, FCCE[GINTx], is set.

30.11.1 Interrupt Queues

Interrupt queues are located in external memory. The parameters of each queue are stored in a table. See

Section 30.11.3, “Interrupt Queue Parameter Tables.”

When an interrupt occurs, the CP writes a new entry to the interrupt queue, the V bit is set, and the queue

pointer (INTQ_PTR) is incremented. Once the CP uses an entry with W = 1, it returns to the first entry in

Table 30-41. UNI Statistics Table

Offset

1

1

Offset from UNI_STATT_BASE+PHY#

× 8

Name

Width

Description

0x00

UTOPIAE

Hword

Counts cells dropped as a result of UTOPIA/ATM protocol violations.

Violations include the following:

1. Parity error

2. HEC error

3. Invalid timing of RxSOC.

If RxClav is asserted for the selected PHY, RxSOC should be asserted the

cycle immediately following the assertion of RXENB. A violation occurs if

RxSOC is not asserted at that time (i.e. is late or is missing).

0x02

MIC_COUNT

Hword

Counts misinserted cells dropped as a result of address look-up failure.

0x04

CRC10E_COUNT

Hword

Counts cells dropped as a result of CRC10 failure. AAL5-ABR only.

0x06

—

Hword

Reserved, should be cleared.