Table 9-6. pocmrx field descriptions, 6 discard timer control register (ptcr), Discard timer control register (ptcr) -32 – Freescale Semiconductor MPC8260 User Manual

Page 338: Pocmrx field descriptions -32, Figure 9-19, Table 9-6. des cribes pocmr x

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

9-32

Freescale Semiconductor

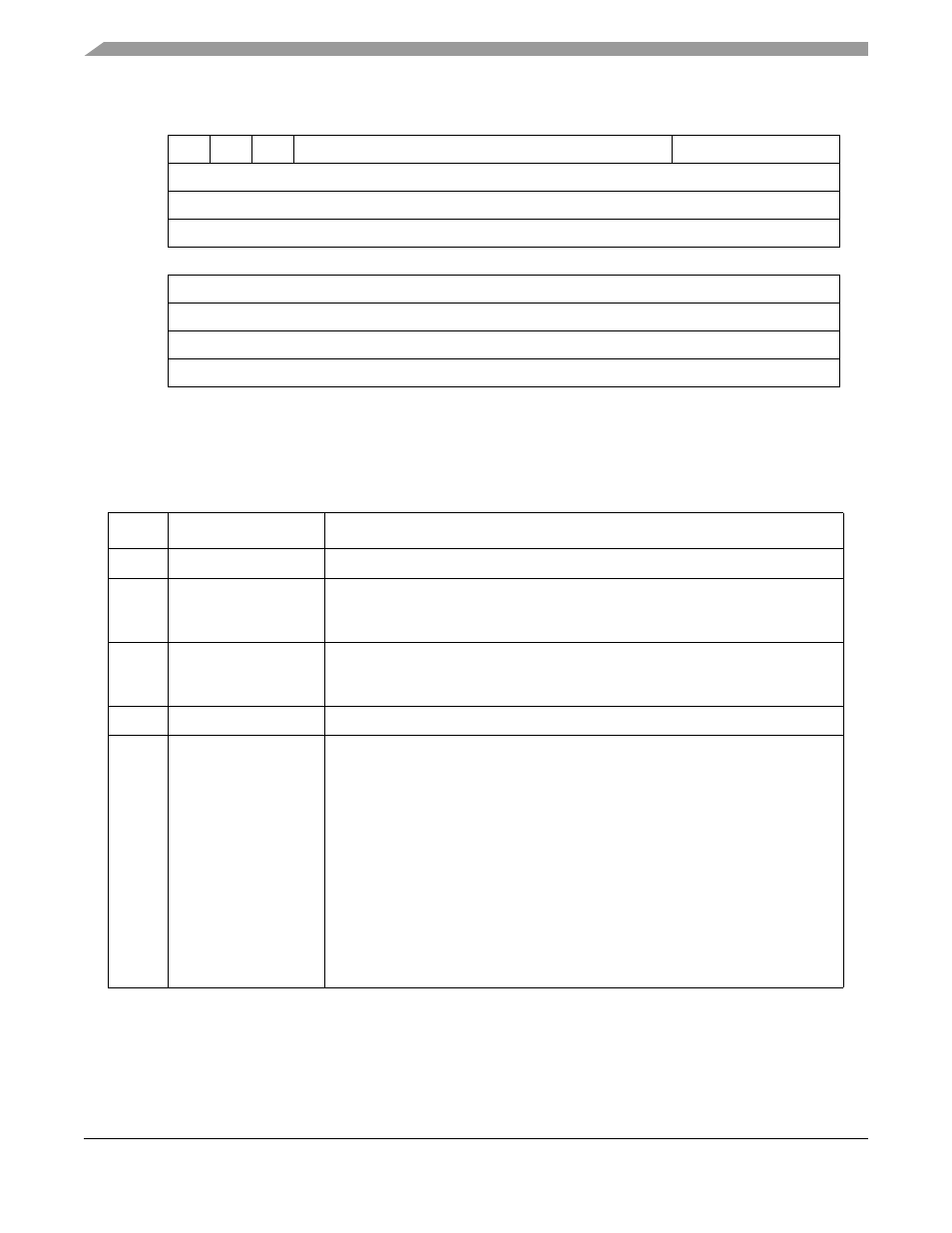

Figure 9-19. PCI Outbound Comparison Mask Registers (POCMR

x)

Table 9-6. describes POCMRx.

9.11.1.6

Discard Timer Control Register (PTCR)

The discard timer control register (PTCR), shown in

, configures the discard timer used to put

a time limit on delayed read transactions from non-prefetchable memory.

31

30

29

28

20

19

16

Field

EN

I/O

PRE

—

CM

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10812 (POCMR0); 0x2082A (POCMR1); 0x10842 (POCMR2)

15

0

Field

CM

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10810 (POCMR0); 0x20828 (POCMR1); 0x10840 (POCMR2)

Table 9-6. POCMR

x Field Descriptions

Bits

Name

Description

31

Enable

This bit enables this address translation

30

I/O

This bit indicates that the translation is to PCI memory or PCI I/O space

0 PCI memory

1 PCI I/O

29

Prefetchable

This bit indicates that the address space is prefetchable, so streaming can occur

0 not prefetchable

1 prefetchable

28–20

—

Reserved, should be cleared.

19–0

Comparison mask

Comparison mask indicates the size of the space to be translated. The value in the

register represents which of the most significant address bits to compare for a

window match. Non-contiguous comparison masks will exhibit unpredictable

behavior.

Examples:

POCMR = 0b0xxx_xxxx_xxxx_xxxx_xxxx_xxxx_xxxx_xxxx

Translation is disabled. All addresses received pass through unaltered.

POCMR = 0b1xxx_xxxx_xxxx_1111_1111_1111_1111_1111

20 bits (physical address bits 31-12) are comparison masked for a 4Kbyte window

size. This is the smallest window size allowed.

POCMR = 0b1xxx_xxxx_xxxx_1111_1111_1111_0000_0000

12 bits (physical address bits 31-20) for a 1Mbyte window size.