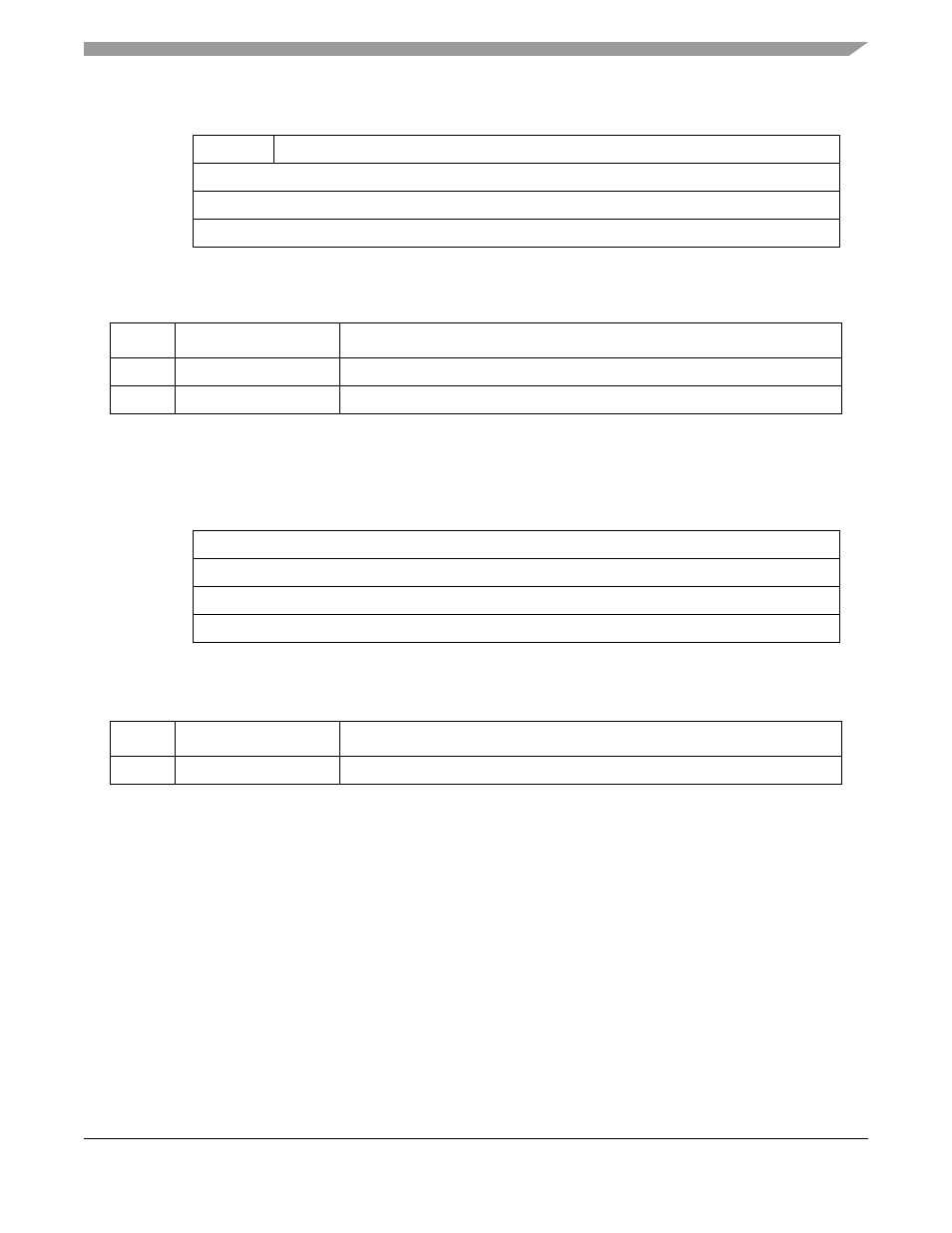

Figure 9-43. header type register, Table 9-30. header type register description, 12 bist control register – Freescale Semiconductor MPC8260 User Manual

Page 359: Figure 9-44. bist control register, Table 9-31. bist control register description, Bist control register -53, Register (pimmrbar) -53, Header type register -53, Header type register description -53, Bist control register description -53

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

9-53

Figure 9-43. Header Type Register

9.11.2.12 BIST Control Register

describe the BIST control register.

Figure 9-44. BIST Control Register

9.11.2.13 PCI Bus Internal Memory-Mapped Registers Base Address Register

(PIMMRBAR)

In agent mode, the PCI bridge provides one base address register called the PCI bus internal

memory-mapped registers base address register (PIMMRBAR) to allow a host processor access to the

PowerQUICC II’s internal memory-mapped registers. Transactions from PCI that “hit” the PIMMRBAR

are translated to the IMMR and sent to the logic that controls the internal memory-mapped registers.

PIMMRBAR is shown in

.

7

6

0

Field

MD

HT

Reset

0000_0000

R/W

R

Addr

0x0E

Table 9-30. Header Type Register Description

Bits

Name

Description

7

Multifunction device

The PCI bridge is not a multifunction PCI device.

6–0

Header type

Identifies the layout of bytes 0x10–0x3F of the configuration address space.

7

0

Field

BIST_CTRL

Reset

0000_0000

R/W

R

Addr

0x0F

Table 9-31. BIST Control Register Description

Bits

Name

Description

7–0

BIST control

Optional register for control and status of built-in self test (BIST)