9 idma commands, 1 start_idma command, Idma commands -27 – Freescale Semiconductor MPC8260 User Manual

Page 671: Start_idma command -27, Section 19.9, “idma commands, Command

SDMA Channels and IDMA Emulation

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

19-27

19.9

IDMA Commands

The user has two commands to control each IDMA channel. These commands are executed through the

CP command register (CPCR); see

19.9.1

START

_

IDMA

Command

The

START

_

IDMA

command is used to start a transfer on an IDMA channel. The user must initialize all

parameters relevant for the correct operation of the channel (IDMAx_BASE and IDMA channel parameter

table) before issuing this command.

To restart the channel operation, the

START

_

IDMA

command can be reissued after every pause in channel

activity. The user must ensure that parameters are correct for the channel to continue operation correctly.

The parameter ISTATE of the IDMA parameter RAM should be cleared before every issue of a

START

_

IDMA

command.

An IDMA pause may occur for one of the following reasons:

•

The channel is out of buffers—IDSR[OB] event is set and an interrupt is generated to the core, if

enabled.

•

DONE was asserted externally and DCM[DT] = 0 (see Table 19-5.). An IDSR[EDN] event is set

and an interrupt is generated to the core, if enabled.

•

STOP

_

IDMA

command was issued.

•

The channel has finished a transfer of a BD with the last bit (L) set.

If the

START

_

IDMA

command is reissued and channel has more buffers to transfer, it restarts transferring

data according to the next BD in the buffer table.

6

SDTB

Source data bus.

0 The source address lies within the 60x bus.

1 The source address lies within the local or PCI buses.

In fly-by mode, should be the same as DDTB.

7-15

—

Reserved, should be cleared.

0x04

0–31

Data

Length

Number of bytes the IDMA transfers. Should be programmed to a value greater than

zero.

Note: When operating with a peripheral that accepts only single bus transactions

(transfer size < 32), data length should be a multiple of the peripheral transfer size

(STS for S/D = 10, or DTS for S/D = 01). Also, there is no error notification if the

data length does not match the buffer sizes.

0x08

0–31

Source

Buffer

Pointer

Holds the address of the associated buffer. Buffers may reside in internal or external

memory. Note that if the source/destination is a device, the pointer should contain the

device address.

In fly-by mode, the pointers should contain the memory address.

0x0C

0–31

Destination

Buffer

Pointer

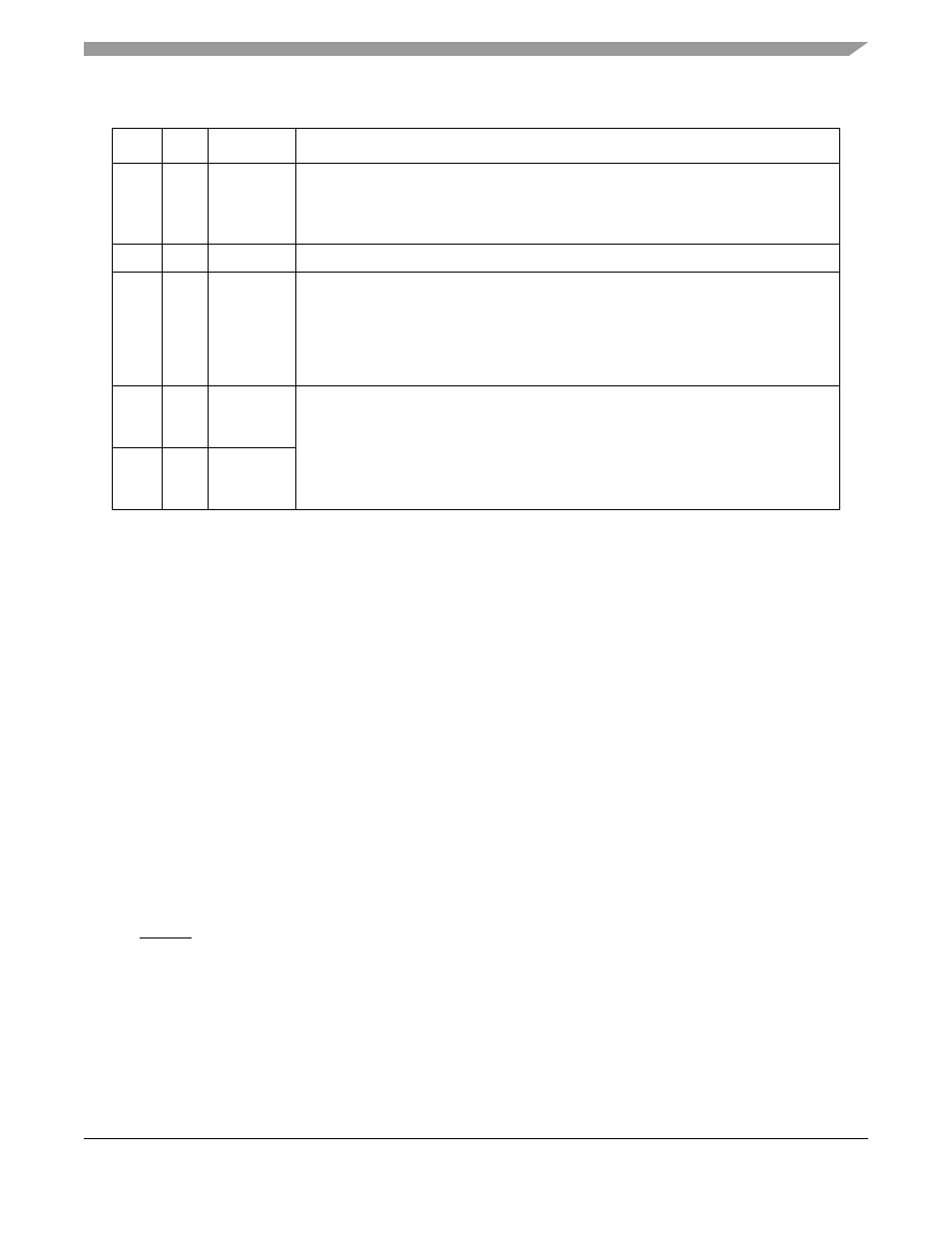

Table 19-10. IDMA BD Field Descriptions (continued)

Offset

Bits

Name

Description