Freescale Semiconductor MPC8260 User Manual

Page 1136

Inverse Multiplexing for ATM (IMA)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

33-34

Freescale Semiconductor

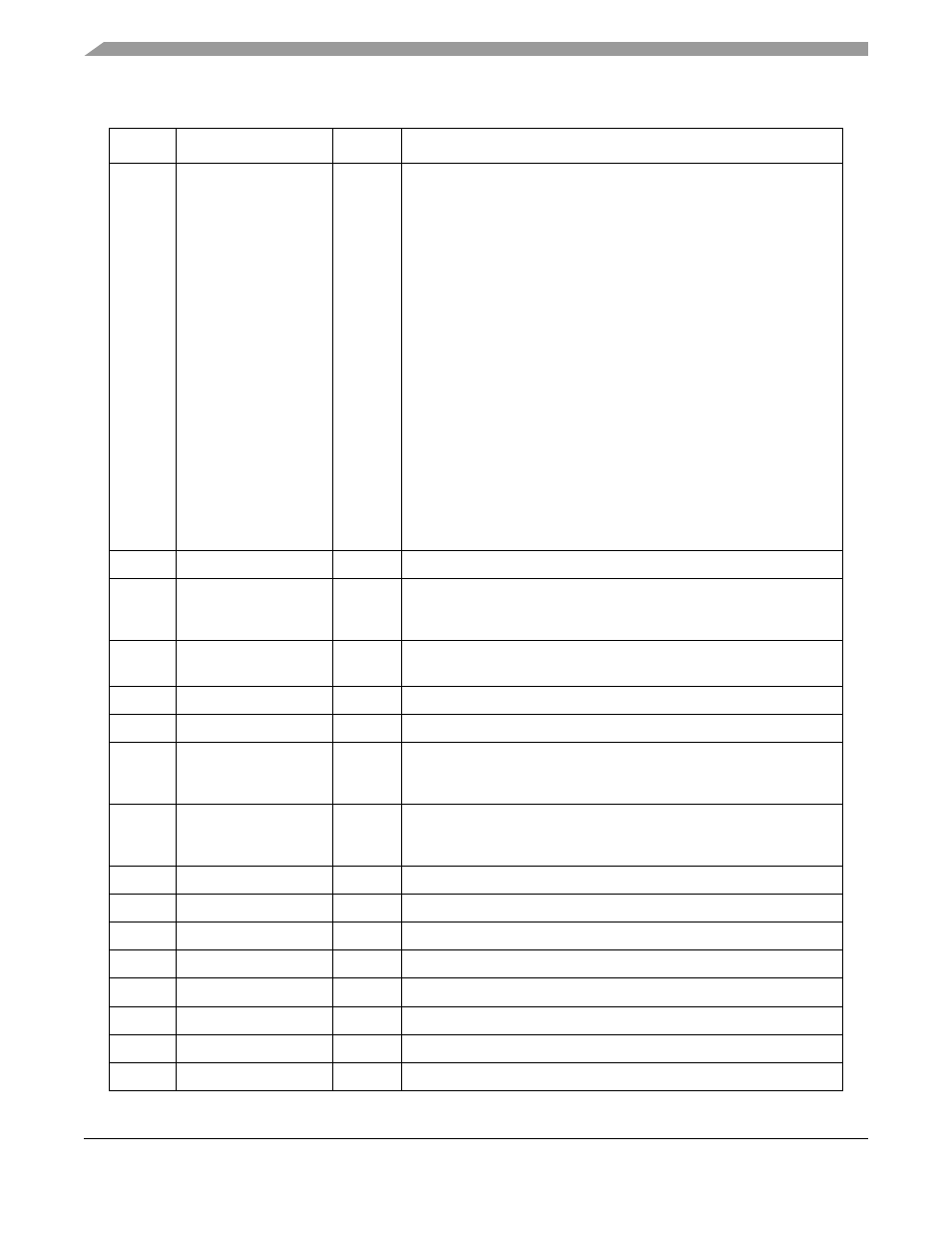

0x08

GROUP STATUS AND

CONTROL

Byte

Bits 7-4: Group State

0000 = Start-up,

0001 = Start-up-Ack,

0010 = Config-Aborted - Unsupported M,

0011 = Config-Aborted - Incompatible Group Symmetry,

0100 = Config-Aborted - Unsupported IMA Version,

0101, 0110 = Reserved for other Config-Aborted reasons in a future

version of the IMA specification,

0111 = Config-Aborted - Other reasons,

1000 = Insufficient-Links,

1001 = Blocked,

1010 = Operational,

Others: Reserved for later use in a future version of the IMA

specification.

Bits 3-2: Group Symmetry Mode

00 = Symmetrical configuration and operation,

01 = Symmetrical configuration and asymmetrical operation (optional),

10 = Asymmetrical configuration and asymmetrical operation

(optional),

11 = Reserved

Bits 1-0: IMA Frame Length (00: M=32, 01: M=64, 10: M=128, 11:

M=256)

0x09

IMA ID

Byte

Bits 7-0: IMA ID

0x0A

STATUS AND

CONTROL CHANGE

INDICATION (SCCI)

Byte

Software must increment this field in the new ICP template whenever a

new ICP template is created.

0x0B

Link Stuff Indication

Byte

Microcode-managed area. Microcode will program this field

dynamically.

0x0C

RX TEST PATTERN

Byte

Bits 7-0: Rx Test Pattern (value from 0 to 255)

0x0D

TX TEST PATTERN

Byte

Bits 7-0: Tx Test Pattern (value from 0 to 255)

0x0E

TX TEST CONTROL

Byte

Bits 7-6: Unused and set to 0

Bit 5: Test Link Command (0: inactive, l: active)

Bits 4-0: Tx LID of test link (0 to 31)

0x0F

TRANSMIT TIMING

INFORMATION

Byte

Bits 7-6: Unused and set to 0

Bit 5: Transmit Clock Mode: (0: ITC mode, 1: CTC mode)

Bits 4-0: Tx LID of the timing reference (0 to 31)

0x10

LINK 3 INFO

Byte

Status and control of link with LID = 3

0x11

LINK 2 INFO

Byte

Status and control of link with LID = 2

0x12

LINK 1 INFO

Byte

Status and control of link with LID = 1

0x13

LINK 0 INFO

Byte

Status and control of link with LID = 0

0x14

LINK 7 INFO

Byte

Status and control of link with LID = 7

0x15

LINK 6 INFO

Byte

Status and control of link with LID = 6

0x16

LINK 5 INFO

Byte

Status and control of link with LID = 5

0x17

LINK 4 INFO

Byte

Status and control of link with LID = 4

Table 33-9. ICP Cell Template (continued)

1

Offset

Name

Width

Description