2 dma status register [0-3] (dmasrx), Figure 9-83. dma status register [0-3] (dmasrx), Dma status register [0–3] (dmasrx) -90 – Freescale Semiconductor MPC8260 User Manual

Page 396: 2 dma status register [0–3] (dmasr, Table 9-67 describes dmasr x fields

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

9-90

Freescale Semiconductor

9.13.1.6.2

DMA Status Register [0–3] (DMASR

x

)

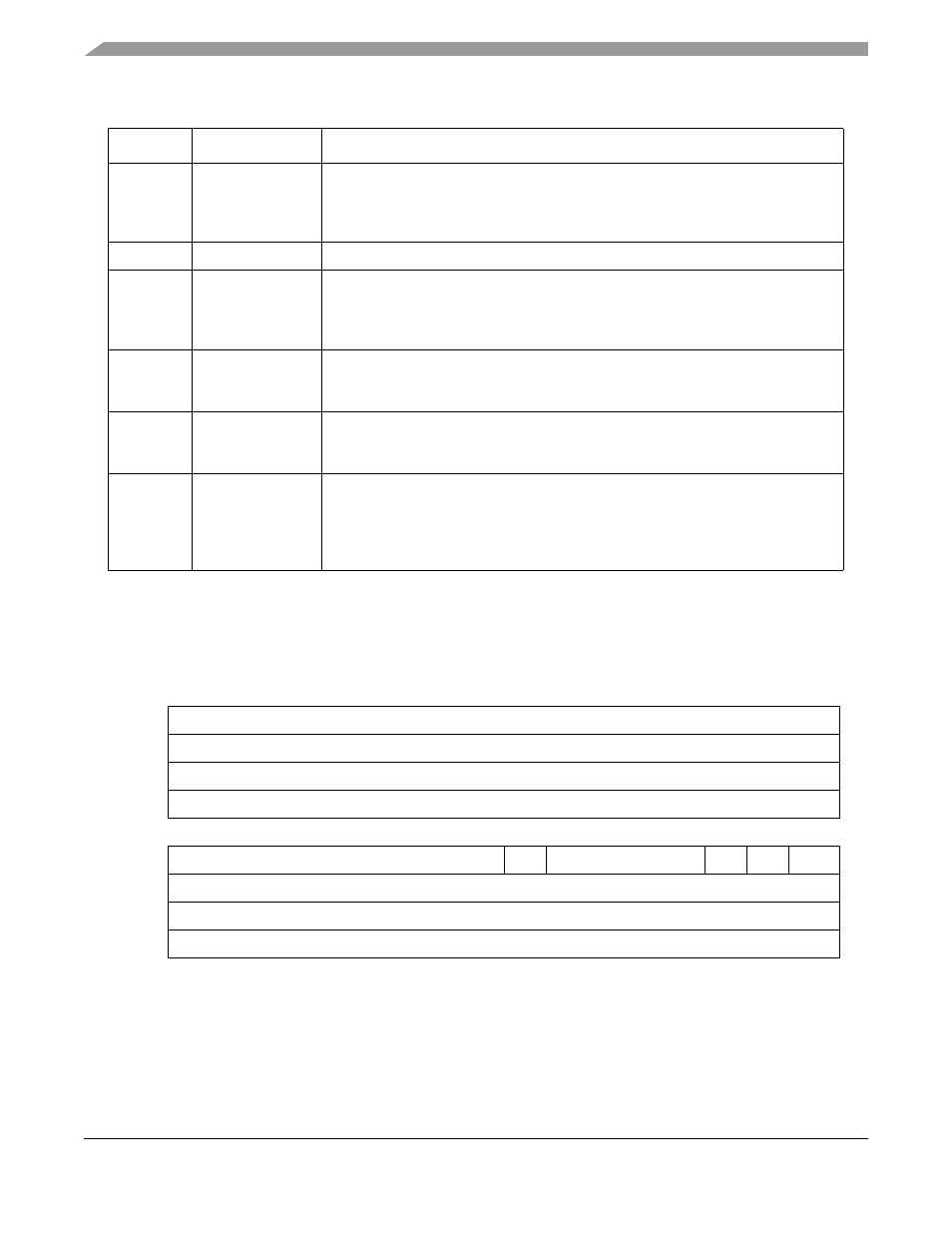

The status register reports various DMA conditions during and after the DMA transfer. Writing a 1 to a

specific set bit clears the bit.

Figure 9-83. DMA Status Register [0–3] (DMASR

x)

describes DMASRx fields.

7

EOTIE

End-of-transfer interrupt enable. When set will generate an interrupt at the

completion of a DMA transfer. No EOT interrupt is generated if this bit is cleared. End

of transfer is defined as the end of a direct mode transfer or in chaining mode, as the

end of the transfer of the last segment of a chain

.

6–4

—

Reserved, should be cleared.

3

TEM

Transfer error mask. This bit determines the DMA response in the event of a transfer

error. If this bit is set, the DMA will complete the transfer regardless of whether a

transfer error occurs (the TE bit is not set). If this bit is clear, the DMA will halt when

a transfer error occurs (TE bit is set).

2

CTM

Channel transfer mode

0 Chaining mode. See

Section 9.13.1.2, “DMA Chaining Mode

.”

Section 9.13.1.1, “DMA Direct Mode

1

CC

Channel continue. When this bit is set, the DMA transfer will restart the transferring

process starting at the Current Descriptor Address. This bit applies only to chaining

mode and is cleared by hardware after every descriptor read.

0

CS

Channel start. A 0-to-1 transition occurring on this bit when the channel is not busy

(SR[CB] bit is 0) will start the DMA process. If the channel is busy and a 0 to 1

transition occurs, then DMA channel will restart from a previous halt condition. A

1-to-0 transition when the channel is busy (CB bit is 1) will halt the DMA process.

Nothing happens if the channel is not busy and a 1 to 0 transition occurs.

31

16

Field

—

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10506(DMASR0); 0x10586 (DMASR1); 0x10606 (DMASR2); 0x10686 (DMASR3)

15

8

7

6

3

2

1

0

Field

—

TE

—

CB

EOSI EOCDI

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10504 (DMASR0); 0x10584(DMASR1); 0x10604 (DMASR2); 0x10684 (DMASR3)

Table 9-66. DMAMR

x Field Descriptions (continued)

Bits

Name

Description