Freescale Semiconductor MPC8260 User Manual

Page 155

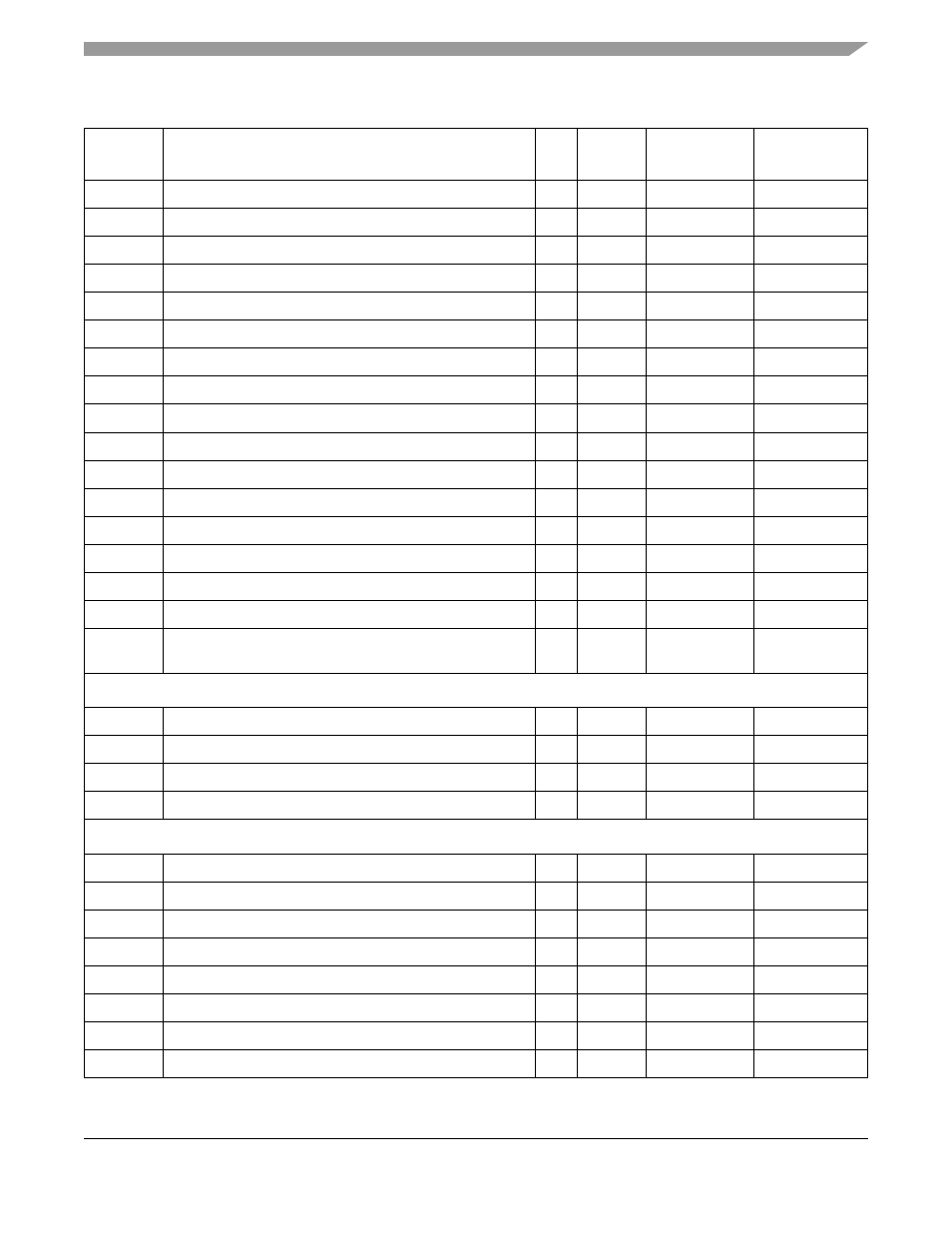

Memory Map

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

3-9

0x10D98

Timer 1 capture register (TCR1)

R/W

16 bits

0x0000

0x10D9A

Timer 2 capture register (TCR2)

R/W

16 bits

0x0000

0x10D9C

Timer 1 counter (TCN1)

R/W

16 bits

0x0000

0x10D9E

Timer 2 counter (TCN2)

R/W

16 bits

0x0000

0x10DA0

Timer 3 mode register (TMR3)

R/W

16 bits

0x0000

0x10DA2

Timer 4 mode register (TMR4)

R/W

16 bits

0x0000

0x10DA4

Timer 3 reference register (TRR3)

R/W

16 bits

0x0000

0x10DA6

Timer 4 reference register (TRR4)

R/W

16 bits

0x0000

0x10DA8

Timer 3 capture register (TCR3)

R/W

16 bits

0x0000

0x10DAA

Timer 4 capture register (TCR4)

R/W

16 bits

0x0000

0x10DAC

Timer 3 counter (TCN3)

R/W

16 bits

0x0000

0x10DAE

Timer 4 counter (TCN4)

R/W

16 bits

0x0000

0x10DB0

Timer 1 event register (TER1)

R/W

16 bits

0x0000

0x10DB2

Timer 2 event register (TER2)

R/W

16 bits

0x0000

0x10DB4

Timer 3 event register (TER3)

R/W

16 bits

0x0000

0x10DB6

Timer 4 event register (TER4)

R/W

16 bits

0x0000

0x10DB8–

0x11017

Reserved

—

608

bytes

—

—

SDMA–General

0x11018

SDMA status register (SDSR)

R/W

8 bits

0x00

0x11019

Reserved

—

24 bits

—

—

0x1101C

SDMA mask register (SDMR)

R/W

8 bits

0x00

0x1101D

Reserved

—

24 bits

—

—

IDMA

0x11020

IDMA 1 event register (IDSR1)

R/W

8 bits

0x00

0x11021

Reserved

—

24 bits

—

—

0x11024

IDMA 1 mask register (IDMR1)

R/W

8 bits

0x00

0x11025

Reserved

—

24 bits

—

—

0x11028

IDMA 2 event register (IDSR2)

R/W

8 bits

0x00

0x11029

Reserved

—

24 bits

—

—

0x1102C

IDMA 2 mask register (IDMR2)

R/W

8 bits

0x00

0x1102D

Reserved

—

24 bits

—

—

Table 3-1. Internal Memory Map (continued)

Address

(offset)

Register

R/W

Size

Reset

Section/Page