Freescale Semiconductor MPC8260 User Manual

Page 880

Multi-Channel Controllers (MCCs)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

28-32

Freescale Semiconductor

of the managing MCC channel for that superchannel (the same MCC channel number used in the

superchannel table entries corresponding to the transmit FIFOs for that superchannel).

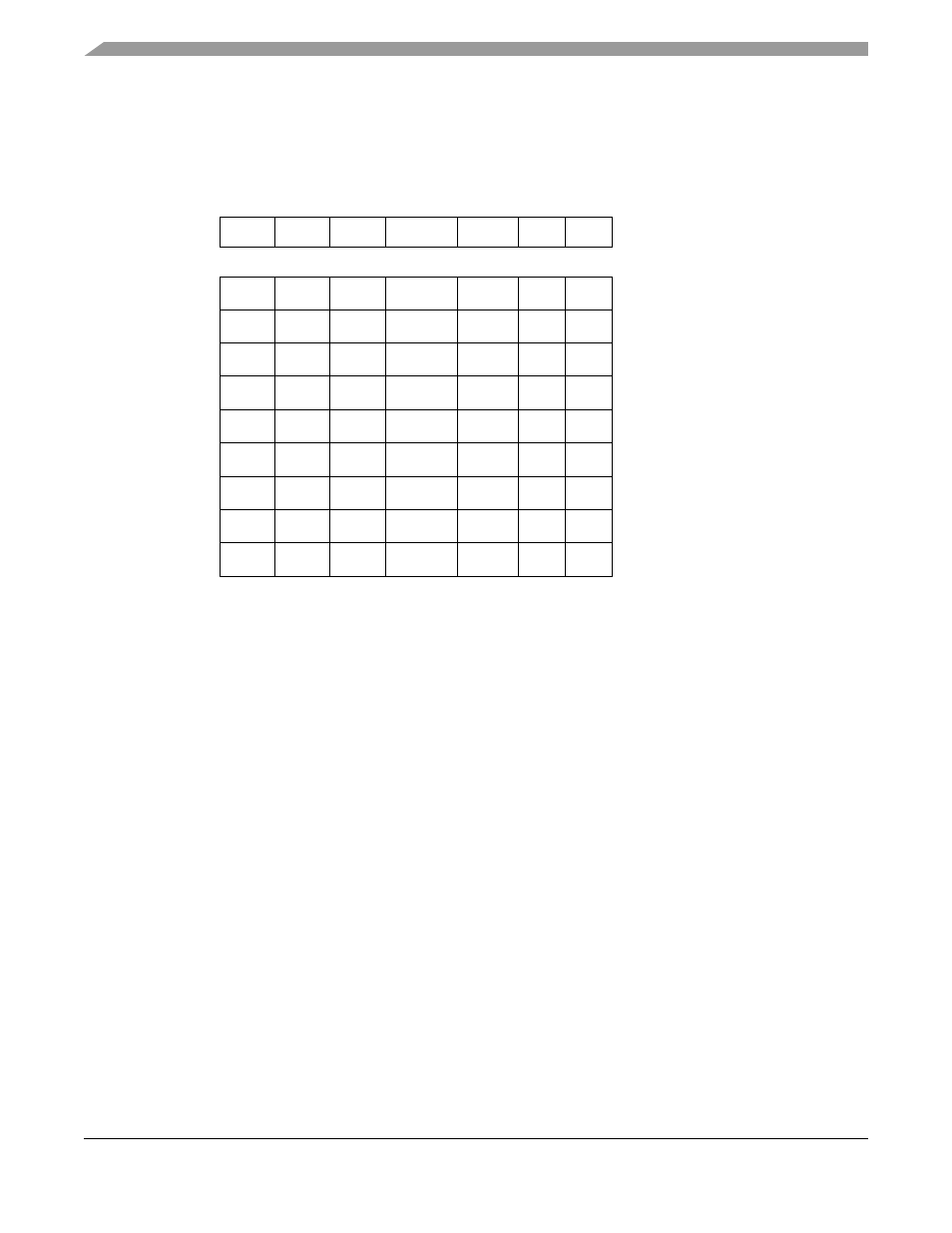

Figure 28-15. Receiver Super Channel with Slot Synchronization Example

shows the SI RAM programming for the same overall configuration as the previous

examples, but in this case it does not matter to the application what timeslot of a superchannel reception

begins on. Thus, slot synchronization is not necessary and the timeslots do not need to be programmed as

superchannelled timeslots and the CNT and BYT fields may be programed normally.

0

1

2

3–10

11–13

14

15

MCC

LOOP SUPER

MCSEL

CNT

BYT

LST

SI RAM Address

1

0

0

0x0

0x0

1

0

Regular Channel

1

0

1

0x1

0x0

1

1

First slot of the super channel

1

0

Super Channel 1

1

0

1

0x2

0x0

1

1

0

Super Channel 2

1

0

1

0x2

0x7

2

2

Regular (not first) slot of the super channel

0

0

Super Channel 2

1

0

1

0x2

0x7

2

0

0

Super Channel 2

1

0

0

0x5

0x0

1

0

Regular Channel

1

0

1

0x1

0x7

2

0

0

Super Channel 1

1

0

1

0x1

0x7

2

0

0

Super Channel 1

1

0

0

0x8

0x0

1

1

Regular Channel

The super channel BD tables are associated with channels 1 and 2

SI RAM