Figure 11-74. exception cycle, Table 11-43. upms attributes example, Exception cycle -89 – Freescale Semiconductor MPC8260 User Manual

Page 507: Upms attributes example -89

Memory Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

11-89

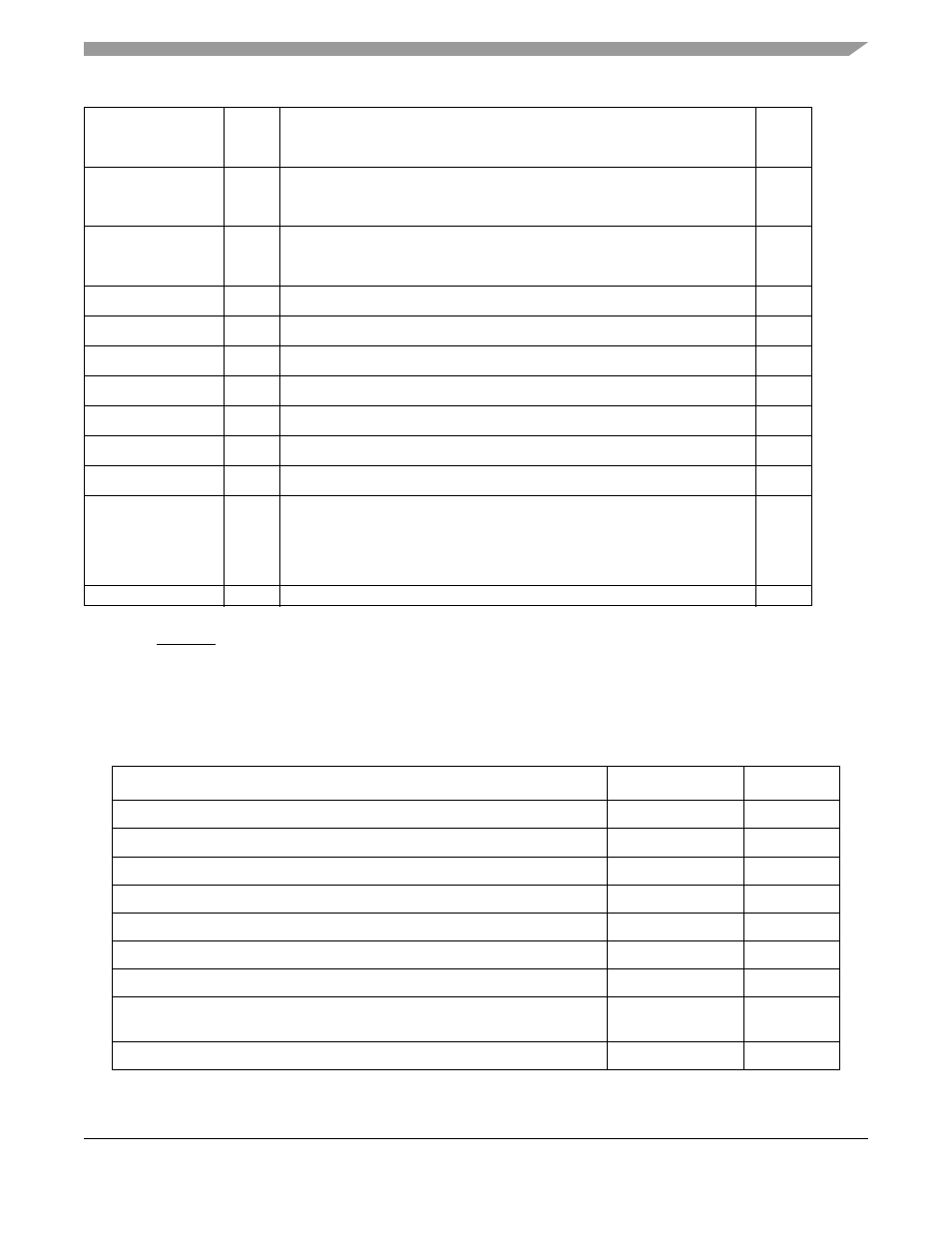

Figure 11-74. Exception Cycle

•

If GPL_4 is not used as an output, the performance for a page read access can be improved by

setting MxMR[GPL_x4DIS]. The following example shows how the burst read access to FPM

DRAM (no LOOP) can be modified using this feature. In this case the configuration registers are

defined in the following way.

cst1

1

Bit 0

cst2

1

Bit 1

cst3

1

Bit 2

cst4

1

Bit 3

bst1

1

Bit 4

bst2

1

Bit 5

bst3

1

Bit 6

bst4

1

Bit 7

g0l0

Bit 8

g0l1

Bit 9

g0h0

Bit 10

g0h1

Bit 11

g1t1

Bit 12

g1t3

Bit 13

g2t1

Bit 14

g2t3

Bit 15

g3t1

Bit 16

g3t3

Bit 17

g4t1

Bit 18

g4t3

Bit 19

g5t1

Bit 20

g5t3

Bit 21

redo[0]

Bit 22

redo[1]

Bit 23

loop

0

Bit 24

exen

0

Bit 25

amx0

0

Bit 26

amx1

0

Bit 27

na

0

Bit 28

uta 0

Bit 29

todt

1

Bit 30

last

1

Bit 31

EXS

Table 11-43. UPMs Attributes Example

Explanation

Field

Value

Machine select UPMA

BR

x

[MS]

0b100

Port size 64-bit

BR

x

[PS]

0b00

No write protect (R/W)

BR

x

[WP]

0b0

Refresh timer value (1024 refresh cycles)

PURT[PURT]

0x0C

Refresh timer enable

M

x

MR[RFEN]

0b1

Address multiplex size

M

x

MR[AM

x

]

0b010

Disable timer period

M

x

MR[DS

x

]

0b01

Select between GPL4 and UPMWAIT = UPMWAIT, data sampled at clock

negative edge

M

x

MR[GPL_x4DIS]

0b1

Burst inhibit device

OR

x

[BI]

0b0