2 data transfer types as programmed in dcm, Data transfer types as programmed in dcm -21, Idma channel data transfer operation -21 – Freescale Semiconductor MPC8260 User Manual

Page 665: Table 19-6

SDMA Channels and IDMA Emulation

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

19-21

19.8.2.2

Data Transfer Types as Programmed in DCM

summarizes the types of data transfers according to the DCM programming.

12

ERM

External request mode.

0 The CP transfers continuously, as if an external level request is asserted, regardless of the

DREQ signal assertion. The CP stops the transfer when there are no more valid BDs or after

a

STOP

_

IDMA

command is issued. DONE assertion by a external device is ignored.

1 The CP responds to DREQ as configured (edge/level) by performing single- or dual-address

transfers. The CP also responds to DONE assertions.

Note: Memory-to-memory transfers (S/D=00) with external request (ERM=1) is allowed, but

DONE assertion is not supported in this mode (DONE should be disabled).

13

DT

DONE treatment:

0 After external DONE assertion, the IDMA ignores further DREQ assertions. The CP closes

the current BD and IDMA stops.

START

_

IDMA

command should be issued before assertion of

another DREQ.

1 After external DONE assertion, the CP closes the current BD. The IDMA continues to the

next BD when DREQ is asserted.

14–1

5

S/D

Source/destination is a peripheral device or memory. See Table 19-6..

00 Read from memory, write to memory.

10 Read from peripheral, write to memory.

01 Read from memory, write to peripheral.

11 Reserved

When a device is a peripheral:

• DACK is asserted during transfers to/from it.

• It may assert DONE to terminate all accesses to/from it.

• It can be operated in fly-by mode—respond to DACK ignoring the address.

• It gets highest DMA priority on the bus arbiter and the lowest DMA latency available.

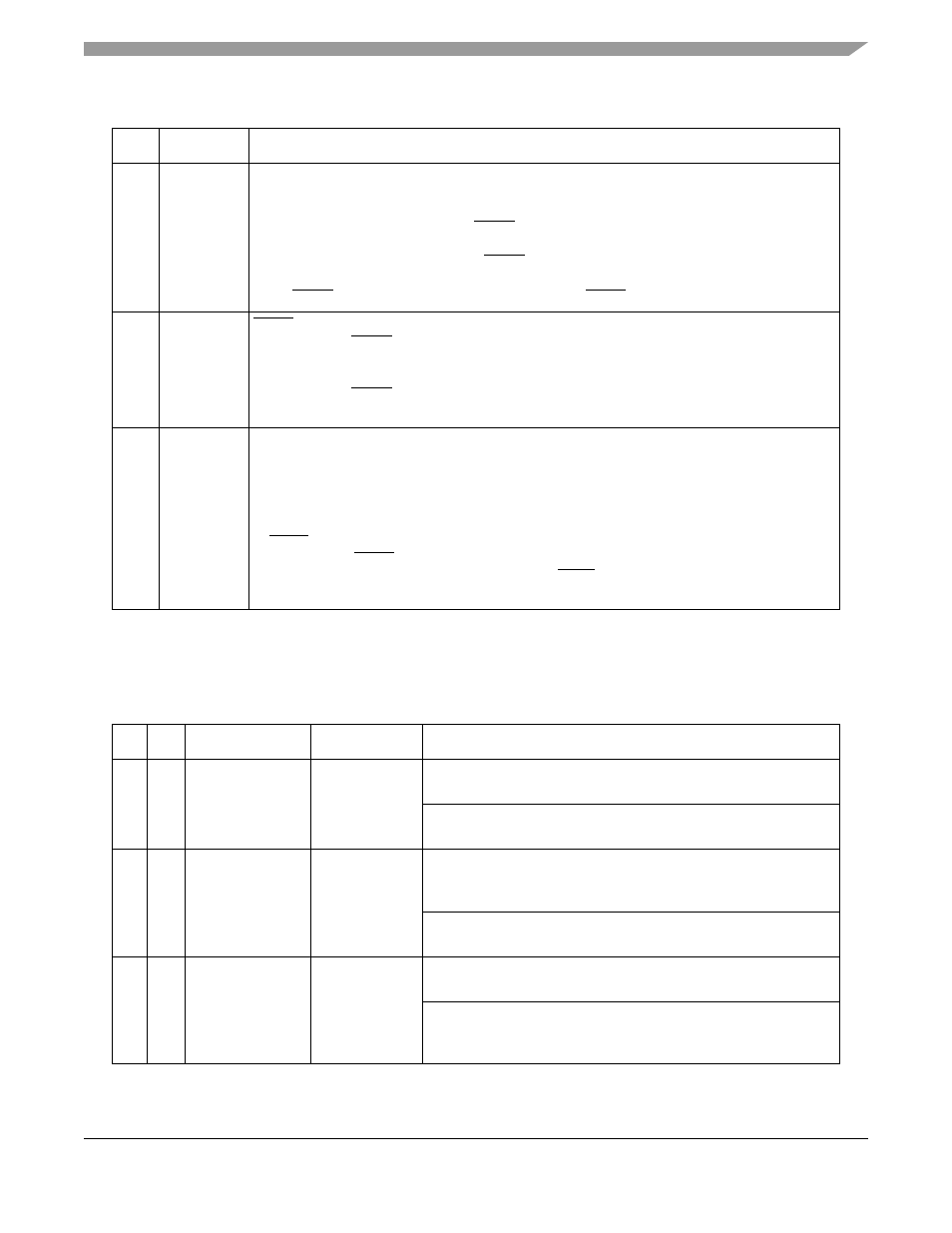

Table 19-6. IDMA Channel Data Transfer Operation

S/D

FB

Read From

Write To

Description (Steady-State Operation)

01

0

Memory

(STS = SS_MAX)

Peripheral

(DTS = port size

or 32)

Read from memory: Filling internal buffer in one DMA transfer.

On the bus: one burst or more, depends on STS

Write to peripheral: In smaller transfers until internal buffer empties.

On the bus: singles or burst, depends on DTS

10

0

Peripheral

(STS = port size or

32)

Memory

(DTS =

SS_MAX)

Read from peripheral: Filling internal buffer in several DMA

transfers.

On the bus: singles or burst, depends on STS

Write to memory: in one DMA transfer, internal buffer empties.

On the bus: one burst or more, depends on DTS

00

0

Memory

(STS = SS_MAX)

Memory

(DTS =

SS_MAX or

less)

Read from memory: Filling internal buffer in one DMA transfer.

On the bus: one burst or more, depends on STS

Write to memory: in one transfer or more until internal buffer

empties.

On the bus: singles or bursts, depends on DTS

Table 19-5. DCM Field Descriptions (continued)

Bits

Name

Description