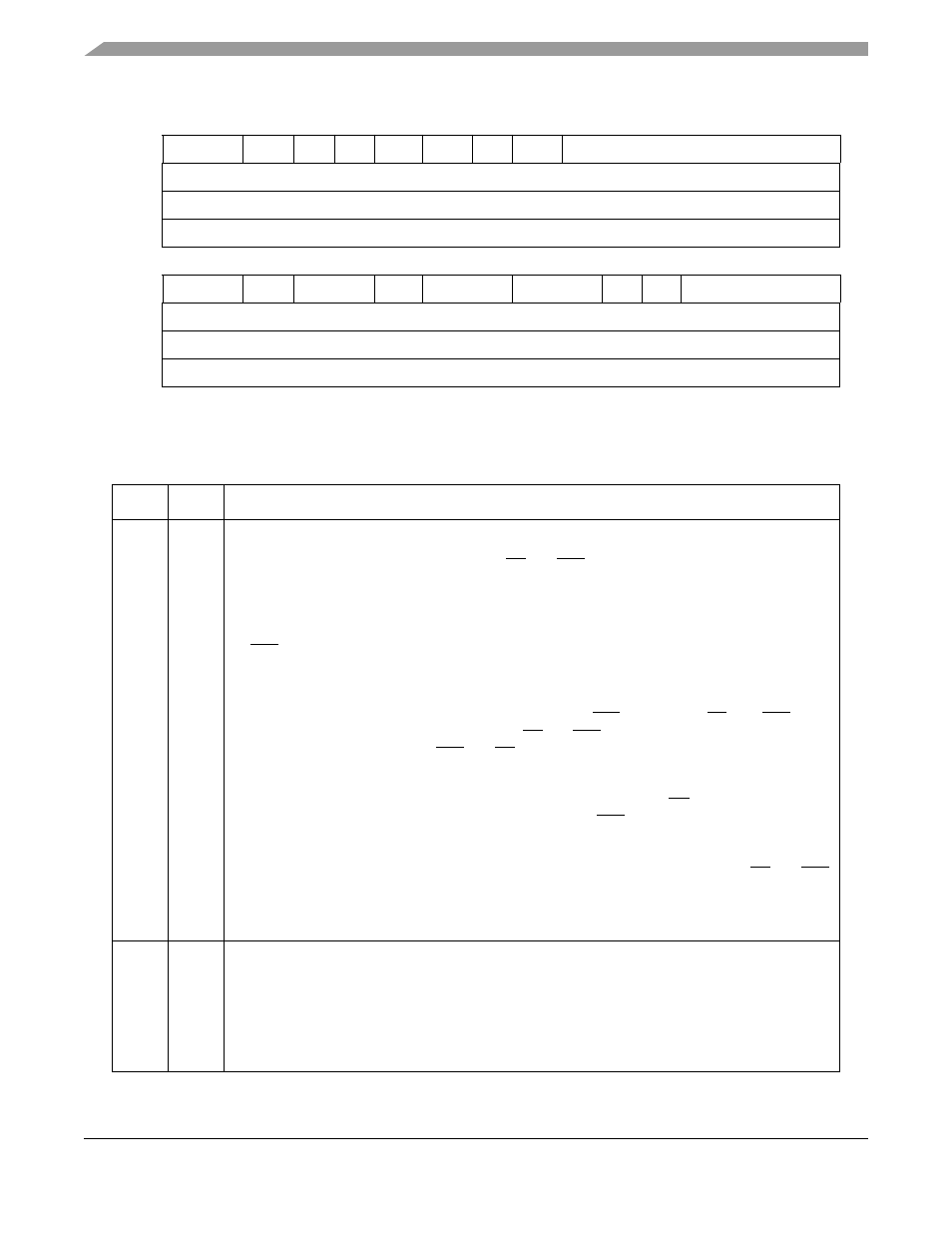

Figure 29-2. general fcc mode register (gfmr), General fcc mode register (gfmr) -4, Gfmr register field descriptions -4 – Freescale Semiconductor MPC8260 User Manual

Page 902: Table 29-2. describes gfmr fields

Fast Communications Controllers (FCCs)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

29-4

Freescale Semiconductor

Table 29-2. describes GFMR fields.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

DIAG

TCI

TRX

TTX

CDP

CTSP CDS CTSS

—

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x0x11300 (GFMR1), 0x0x11320(GFMR2), 0x0x11340(GFMR3)

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Field

SYNL

RTSM

RENC

REVD

TENC

TCRC

ENR ENT

MODE

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x11302 (GFMR1), 0x11322 (GFMR2), 0x11342 (GFMR3)

Figure 29-2. General FCC Mode Register (GFMR)

Table 29-2. GFMR Register Field Descriptions

Bits

Name Description

0–1

DIAG

Diagnostic mode.

00 Normal operation—Receive data enters through RXD, and transmit data is shifted out through

TXD. The FCC uses the modem signals (CD and CTS) to automatically enable and disable

transmission and reception. Timings are shown in

Section 29.11, “FCC Timing Control

01 Local loopback mode—Transmitter output is connected internally to the receiver input, while the

receiver and the transmitter operate normally. RXD is ignored. Data can be programmed to

appear on TXD, or TXD can remain high by programming the appropriate parallel port register.

RTS can be disabled in the appropriate parallel I/O register. The transmitter and receiver must

use the same clock source, but separate CLK

x

pins can be used if connected to the same

external clock source.

If external loopback is preferred, program DIAG for normal operation and externally connect TXD

and RXD. Then, physically connect the control signals (RTS connected to CD, and CTS

grounded) or set the parallel I/O registers so CD and CTS are permanently asserted to the FCC

by configuring the associated CTS and CD pins as general-purpose I/O.; see

.”

10 Automatic echo mode—The channel automatically retransmits received data, using the receive

clock provided. The receiver operates normally and receives data if CD is asserted. The

transmitter simply transmits received data. In this mode, CTS is ignored. The echo function can

also be accomplished in software by receiving buffers from an FCC, linking them to TxBDs, and

transmitting them back out of that FCC.

11 Loopback and echo mode—Loopback and echo operation occur simultaneously. CD and CTS

are ignored. Refer to the loopback bit description for clocking requirements.

For TDM operation, the diagnostic mode is selected by SI

x

MR[SDM

x

]; see

.”

2

TCI

Transmit clock invert

0

Normal operation.

1

The FCC inverts the internal transmit clock.

The edge on which the FCC outputs the data depends on the protocol:

• In HDLC and Transparent mode, when TCI=0, data is sent on the falling edge; when TCI=1, on

the rising edge.

• In Ethernet mode, when TCI=0, data is sent on the rising edge; when TCI=1, on the falling edge.