Table a-3 – Freescale Semiconductor MPC8260 User Manual

Page 1300

Register Quick Reference Guide

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

A-2

Freescale Semiconductor

lists supervisor-level SPRs defined by the PowerPC architecture.

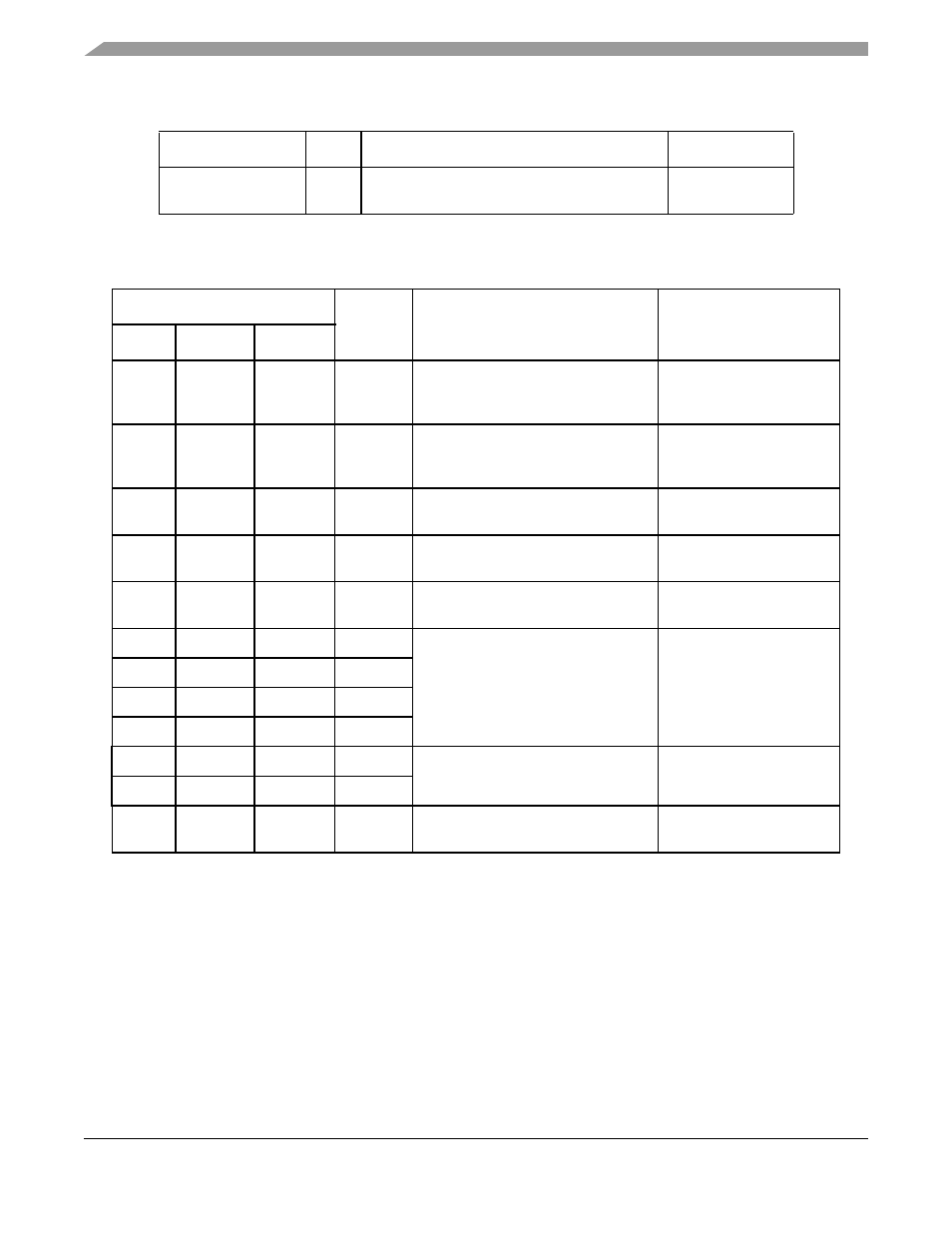

Table A-3. Supervisor-Level PowerPC Registers

Description

Name

Comments

Serialize Access

Machine state register

MSR

See the

Programming Environments Manual

and

MPC603e RISC Microprocessor User’s Manual

Write fetch sync

Table A-4. Supervisor-Level PowerPC SPRs

SPR Number

Name

Comments

Serialize Access

Decimal

SPR[5–9]

SPR[0–4]

18

00000

10010

DSISR

See the

Programming Environments

Manual

Write: Full sync

Read: Sync relative to

load/store operations

19

00000

10011

DAR

See the

Programming Environments

Manual

Write: Full sync

Read: Sync relative to load/

store operations

22

00000

10110

DEC

See the

Programming Environments

Manual

Write

26

00000

11010

SRR0

See the

Programming Environments

Manual

Write

27

00000

11011

SRR1

See the

Programming Environments

Manual

Write

272

01000

10000

SPRG0

See the

Programming Environments

Manual

Write

273

01000

10001

SPRG1

274

01000

10010

SPRG2

275

01000

10011

SPRG3

284

01000

11100

TBL write

1

1

Any read (mftb) to this address causes an implementation-dependent software emulation exception.

See the

Programming Environments

Manual

Write (as a store)

285

01000

11101

TBU write

1

287

01000

11111

PVR

Section 2.3.1.2.4, “Processor Version

Register (PVR)

.”

No (read-only register)